高速轉(zhuǎn)換器時鐘分配器件的端接

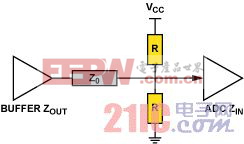

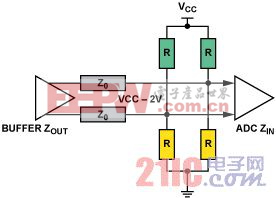

端接不當(dāng)使回聲的幅度隨著時間而變化,因此t也會隨時間變化。端接的時間常數(shù)也會影響回聲脈沖的形狀和寬度。基于以上原因,反射引起的附加抖動,從形狀看類似增加經(jīng)典抖動的高斯特性。為了避免抖動和時鐘質(zhì)量降低的不利影響,需要使用表1中總結(jié)的恰當(dāng)信號端接方法。Z0是傳輸線的阻抗;ZOUT 是驅(qū)動器的輸出阻抗,ZIN 是接收器的輸入阻抗。僅顯示CMOS和PECL/LVPECL電路。

表1. 時鐘端接

表1. 時鐘端接

方法 | 描述 | 優(yōu)勢 | 弱點 | 備注 |

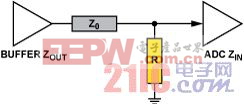

串行端接 | CMOS  實際上,因為阻抗會隨頻率動態(tài)變化,難以達到阻抗匹配,所以緩沖器輸出端可以省去電阻(R)。 | 低功耗解決方案(沒有對地的吸電流) 很容易計算R的值 R (Z0 – ZOUT). | 上升/下降時間受RC電路的影響,增加抖動。 只對低頻信號有效。 | CMOS驅(qū)動器 不適合高頻時鐘CMOS drivers.信號。 適合低頻時鐘信號和非常短的走線。 |

下拉電阻 | CMOS  | 非常簡單(R = Z0) | 高功耗 | 不推薦 |

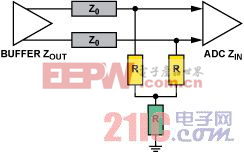

LVPECL  | 簡單的3電阻解決方案。 就節(jié)能而言稍好一點,相對于4電阻端接來說節(jié)省一個電阻。 | 推薦。 端接電阻盡可能靠近PECL接收器放置。 | ||

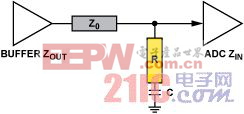

交流端接 | CMOS  | 沒有直流功耗。 | 為避免較高功耗,C應(yīng)該很小,但也不能太小而導(dǎo)致吸電流。 | |

LVPECL  | 交流耦合允許調(diào)整偏置電壓。避免電路兩端之間的能量流動。 | 交流耦合只推薦用于平衡信號(50%占空比的時鐘信號)。 | 交流耦合電容的ESR值和容值應(yīng)該很低。 | |

電阻橋 | CMOS  | 功耗實現(xiàn)合理的權(quán)衡取舍。 | 單端時鐘用兩個器件。 | |

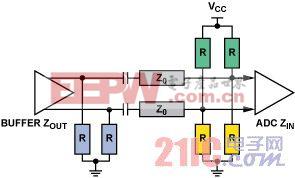

LVPECL  | 差分輸出邏輯用4個外部器件。 | 3.3V LVPECL驅(qū)動器廣泛應(yīng)用端接。 |

關(guān)鍵詞:

器件

分配

時鐘

轉(zhuǎn)換器

高速

相關(guān)推薦

技術(shù)專區(qū)

- FPGA

- DSP

- MCU

- 示波器

- 步進電機

- Zigbee

- LabVIEW

- Arduino

- RFID

- NFC

- STM32

- Protel

- GPS

- MSP430

- Multisim

- 濾波器

- CAN總線

- 開關(guān)電源

- 單片機

- PCB

- USB

- ARM

- CPLD

- 連接器

- MEMS

- CMOS

- MIPS

- EMC

- EDA

- ROM

- 陀螺儀

- VHDL

- 比較器

- Verilog

- 穩(wěn)壓電源

- RAM

- AVR

- 傳感器

- 可控硅

- IGBT

- 嵌入式開發(fā)

- 逆變器

- Quartus

- RS-232

- Cyclone

- 電位器

- 電機控制

- 藍(lán)牙

- PLC

- PWM

- 汽車電子

- 轉(zhuǎn)換器

- 電源管理

- 信號放大器

評論