基于現(xiàn)代DSP技術的QPSK調(diào)制器的設計

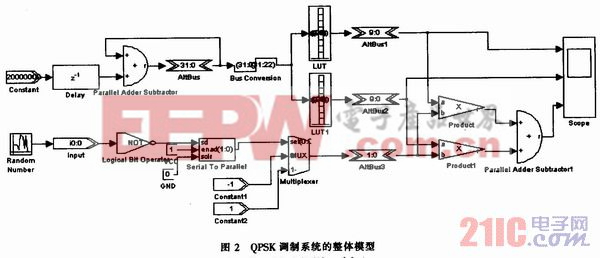

研究采用QuartusII6.1、DSP Builder6.1和Madab Rb2006作為FPGA的設計及測試平臺。因此,在設計的過程中可以很方便的調(diào)用DSP-Bbuilder和Simulink庫中的圖形模塊來建立硬件模型,輸入信號也可方便的調(diào)用Simulink模塊。依據(jù)QPSK的基本原理,可以快速的建立QPSK模型。要完成QPSK的建模,首先打開MATLAB,在命令窗口輸入“Simulink”進入圖形化仿真建模環(huán)境,新建一個仿真模型。依照圖1的原理圖設計,建立模型如圖2所示。本文引用地址:http://www.104case.com/article/150838.htm

圖2中,由頻率字、延時器、加法器和兩個LUT組成正交信號發(fā)生器,產(chǎn)生兩個正交的載波信號。隨機信號發(fā)生模塊產(chǎn)生隨機信號,經(jīng)過反相器形成數(shù)字基帶信號,經(jīng)過串并轉(zhuǎn)換模塊變?yōu)椴⑿行盘枺俳?jīng)過多路選擇器模塊輸出+1和-1,然后和正交信號發(fā)生器產(chǎn)生的正交載波信號相乘,最后在加法器中進行相加實現(xiàn)QPSK調(diào)制。

3 系統(tǒng)仿真與硬件測試

3.1 系統(tǒng)仿真

完成整個設計后,設置仿真時間,開始仿真。設置Simulik的仿真停止時間為2 000,仿真步進設為自動。仿真結果如圖3,圖中前兩欄為正交波信號,最后一欄為QPSK已調(diào)信號。

3.2 硬件測試

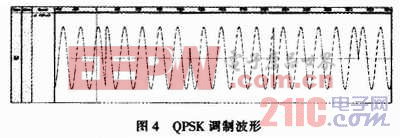

在Simulink中完成仿真驗證后,需要把設計轉(zhuǎn)到硬件上去實現(xiàn)。這是整個DSP Builder設計流程中最為關鍵的一步,可獲得對特定FIGA芯片的VHDL代碼。雙擊QPSK模型中的SignalCompiler,點擊分析按鈕,檢查模型無錯誤后,打開SignalCompiler窗口,在圖中設置好相應項后,依次點擊1、2、3 3個按鈕,逐項執(zhí)行VHDL文件轉(zhuǎn)換、綜合、適配,即可將.mdl文件轉(zhuǎn)換為.vhd文件。同時,在工作目錄生成的文件中有tb_qpsk.tcl和tb_qpsk.v文件。tb_qpsk.v文件是在QuartusII中要用到的工程文件,tb_qpsk.tcl文件是要在Modesim進行RTL級仿真用到的測試代碼。仿真完成后,在QuartusII中指定器件管腳、進行編譯、下載。最后進行硬件的下載,連接好FPGA開發(fā)板即可。本文采用的硬件是Cyclone系列芯片EP2C35F672C6N。圖4是在QuartusII中QPSK的已調(diào)波形,與仿真波形基本一致。由圖可以看出,有4個相位跳變點,正

確地反映了QPSK調(diào)制的特點。

4 結論

本文利用了現(xiàn)代DSP技術的功能,在Simulink的環(huán)境下實現(xiàn)了QPSK的建模,給出了具體模型,從而避免了VHDL程序的編制,縮短了周期,提高了效率。采用該法,極大地提高了電子系統(tǒng)設計的靈活性和通用性。仿真結果和硬件實現(xiàn)都驗證了該方案的正確性。

評論