基于FPGA+DSP的高速中頻采樣信號(hào)處理平臺(tái)的實(shí)現(xiàn)

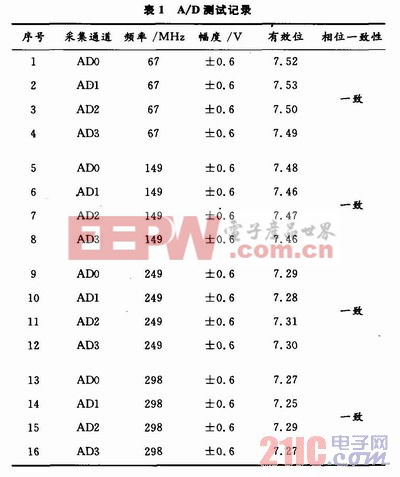

2.1 A/D采樣的有效位數(shù)

有效位數(shù)是用來(lái)表述A/D器件的一項(xiàng)總體指標(biāo),對(duì)精確評(píng)價(jià)系統(tǒng)性能非常重要。對(duì)于A/D采樣有效位的測(cè)試,采用A/D器件的最大量程輸入,在FPGA中取得數(shù)據(jù),用Matlab來(lái)對(duì)數(shù)據(jù)處理進(jìn)行計(jì)算得到的。四路A/D采樣通道有效位的測(cè)試數(shù)據(jù)如表1所示。本文引用地址:http://www.104case.com/article/150836.htm

2.2 A/D通道間相位恒定

A/D通道間的相位恒定指標(biāo)直接測(cè)試比較困難,在平臺(tái)設(shè)計(jì)中已經(jīng)保證了同一芯片兩路A/D通道間的相位差是恒定的,只要測(cè)試兩片A /D芯片輸出時(shí)鐘相位差是否恒定即可判定。表1中也顯示了兩片A/D器件輸出時(shí)鐘的相位差測(cè)試結(jié)果。

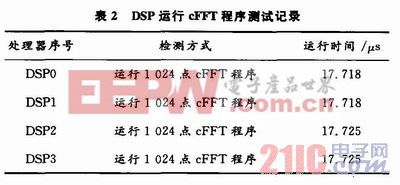

2.3 DSP運(yùn)算速度

DSP的運(yùn)算速度和精度決定著系統(tǒng)的數(shù)據(jù)處理能力,同時(shí)也會(huì)對(duì)整個(gè)系統(tǒng)的性能和結(jié)構(gòu)產(chǎn)生重要的影響。DSP的處理能力可以用1 024點(diǎn)的復(fù)數(shù)FFT計(jì)算時(shí)間進(jìn)行比較。Link口傳遞速度的測(cè)試,可以將Link口的工作時(shí)鐘設(shè)定在600 MHz,按4 b進(jìn)行數(shù)據(jù)傳遞,如果接收到數(shù)據(jù)沒(méi)有錯(cuò)誤,即可認(rèn)定Link口的工作速率可以達(dá)到600 MB/s。經(jīng)過(guò)測(cè)試,在工作頻率為600 MHz,按4 b進(jìn)行數(shù)據(jù)傳遞的情況下,各個(gè)Link均通過(guò)測(cè)試,也就是說(shuō)每個(gè)Link口工作速率都可以達(dá)到600 MB/s。經(jīng)過(guò)測(cè)試,平臺(tái)上兩個(gè)光口的傳輸速度均達(dá)到了2.5 Gb/s。DSP運(yùn)算速度測(cè)試結(jié)果見(jiàn)表2。

3 結(jié)語(yǔ)

通過(guò)上述測(cè)試結(jié)果可以看出,本平臺(tái)設(shè)計(jì)合理,FPGA與DSP的結(jié)合使用,能充分發(fā)揮各自的優(yōu)勢(shì),實(shí)現(xiàn)對(duì)高速、多路、海量信號(hào)的實(shí)時(shí)處理。另外,高度集成化設(shè)計(jì),大大減少了平臺(tái)所占用的空間體積,也使功耗大大減小。平臺(tái)在兵器某所項(xiàng)目驗(yàn)證中,接入實(shí)際雷達(dá)信號(hào)進(jìn)行測(cè)試,各項(xiàng)指標(biāo)均達(dá)到了設(shè)計(jì)要求。

評(píng)論