用VHDL設計有限狀態機的方法

end if;

end process state_clocked;

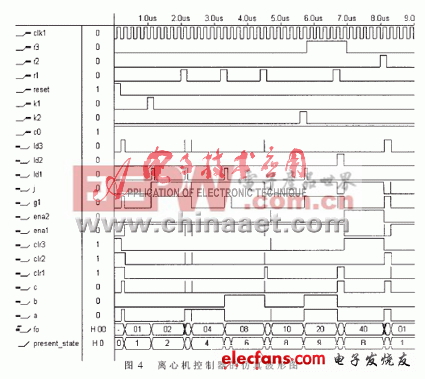

end state_machine;利用EDA軟件MAX+plus Ⅱ對該程序進行編譯、仿真,其仿真波形見圖4。

從圖4仿真波形圖上可以看出,狀態機的輸出信號有許多“毛刺”產生。如何消除這些“毛刺”是下面將討論的問題。

在同步電路中,一般情況下“毛刺”不會產生重大影響。因為“毛刺”僅發生在時鐘有效邊沿之后的一小段時間內,只要在下一個時鐘有效邊沿到來之前“毛刺”消失即可。但是,由于狀態機的輸出信號都是作為其它功能模塊的控制信號,如果這些控制信號作為異步控制(如本系統中的CLR)、三態使能控制或時鐘信號來使用,則將會使受控模塊發生誤動作,造成系統工作混亂。因此,在這種情況下必須保證狀態機的輸出沒有“毛刺”。

消除狀態機輸出信號的“毛刺”有以下三種方案:

·在狀態機輸出信號較少的情況下,直接把狀態作為輸出信號;

·對于順序遷移的狀態機,選擇雷格碼作為狀態編碼;

·在Moore型或Mealy型狀態機基礎上,用時鐘同步輸出信號。

本設計采用后兩種方案,較簡便。雷格碼的特點是:當狀態機改變狀態時,狀態向量中僅1位發生變化。與前面用可枚舉類型定義的狀態變量不同,現在選用常數來指定各狀態變量的取值為格雷碼。修改部分設計程序如下:

若要完全消除狀態機的“毛刺”,則應采用第三種方案。這時,設計程序要作相應改變,狀態的轉移和輸出信號的賦值要寫在同一個時鐘進程中。

綜上所述,采用VHDL設計狀態機,能夠大大降低設計難度。使用雙進程描述風格編寫VHDL設計程序,可以清楚地在一個進程中確定狀態的轉移和對輸出的賦值,而且具有易于建立、理解和維護的優點。特別針對大型或具有大量狀態轉移和輸出信號的狀態機設計,將會更加顯示出它的優勢。對于狀態機輸出信號所產生的“毛刺”,可以按照系統的要求,根據不同的情況采用相應的設計方案予以消除

塵埃粒子計數器相關文章:塵埃粒子計數器原理

評論