CPLD的DSP多SPI端口通信設計

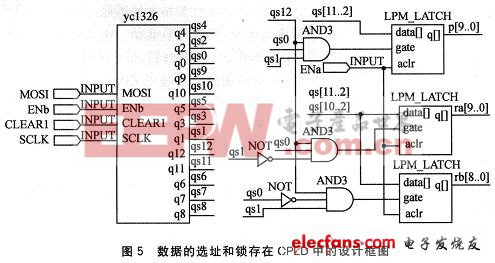

鎖存器的工作特點:當gate引腳上輸入高電平信號時,鎖存器工作開始鎖存總線上的數(shù)據(jù);當gate引腳上是低電平時,鎖存器不工作,即當總線上的數(shù)據(jù)發(fā)生變化時,鎖存器的輸出不發(fā)生變化。由于本設計需要多個參數(shù)傳輸,通過地址選擇的方法把這3個數(shù)據(jù)從一條總線上區(qū)分出來,設置傳輸數(shù)據(jù)的低兩位為地址選擇位。地址選擇位經(jīng)移位寄存器,串并轉(zhuǎn)換,作為三輸入與門的兩個輸入端,進行地址選擇。每次16位的數(shù)據(jù)移位結(jié)束,數(shù)據(jù)穩(wěn)定時,在計數(shù)器高電平作用下,相應gate的引腳上輸出高電平,數(shù)據(jù)鎖存入相應的鎖存器。例如,可以設置低兩位是“11”時,DSP送入PWM電路的是ll位的調(diào)相信號;當?shù)蛢晌辉O置成“01”時,DSP送入PWM電路的是10位調(diào)節(jié)A相占空比的信號;當?shù)蛢晌辉O置成“10”時,DSP送入PWM電路的是10位調(diào)節(jié)B相占空比的信號。由此可以在電路中設計一個三輸人的與門,當16位數(shù)據(jù)傳輸完畢,即在相應gate的引腳上輸出高電平時,數(shù)據(jù)存入對應的鎖存器,如圖5所示。

2.3 DSP與LTC6903的接口配置

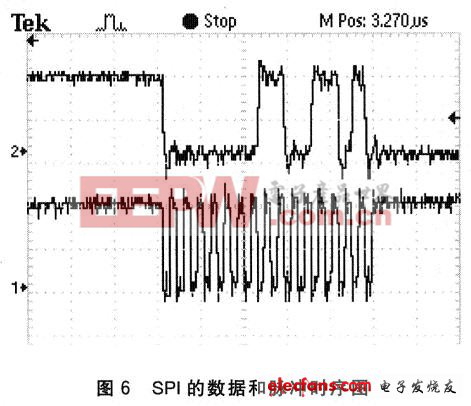

由于LTC6903芯片本身具有SPI接口,需要在DSP的程序中設置相應的SPI寄存器。LTC6903采用上升沿接收,且接收時高位在前,所以需要DSP設置為下降沿傳輸,傳輸時高位在前。在傳輸?shù)倪^程中,在脈沖信號的下降沿數(shù)據(jù)發(fā)生變化,傳輸數(shù)據(jù);在脈沖信號的上升沿數(shù)據(jù)穩(wěn)定,便于LTC6903鎖存數(shù)據(jù),傳輸時序如圖6所示。從圖中可以看出,所要傳輸?shù)臄?shù)據(jù)是十六進制數(shù)019A,下降沿數(shù)據(jù)發(fā)生變化,上升沿數(shù)據(jù)穩(wěn)定,傳輸16位數(shù)據(jù),有16個脈沖。實驗結(jié)果表明,DSP配置是與LTC6903的SPI接口工作時序相匹配的。

3 DSP中SPI的開發(fā)過程

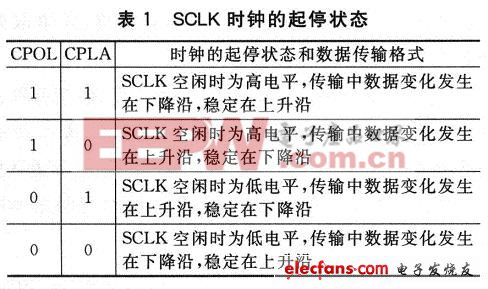

SPI端口數(shù)據(jù)傳輸?shù)奶攸c是:主設備的時鐘信號出現(xiàn)與否決定數(shù)據(jù)傳輸?shù)拈_始,一旦檢測到時鐘信號即開始傳輸,時鐘信號無效后傳輸結(jié)束。這期間,從設備使能時鐘信號的起停狀態(tài)很重要。DSP56F801的SPI端口的時鐘信號起停狀態(tài)如表1所列。在設計中設置的SPI控制寄存器的CPOL和CPLA位是“11”。SCLK空閑時為高電平,傳輸中數(shù)據(jù)變化發(fā)生在下降沿,穩(wěn)定在上升沿。從圖2可看出實現(xiàn)了與CPLD中的移位鎖存電路的匹配,傳輸正確。

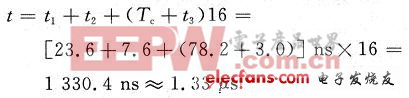

SPI端口協(xié)議要求系統(tǒng)上電復位后,從機先于主機開始工作。如果從機在主機之后開始工作,就有可能丟掉部分時鐘信號,使得從機并不是從數(shù)據(jù)的第一位開始接收,造成數(shù)據(jù)流的不同步。可通過硬件延時或軟件延時的方法,來確保從機先于主機工作。本設計采用軟件延時的辦法來實現(xiàn)數(shù)據(jù)流的同步。這個延時由兩部分組成,一部分是DSP串行輸出數(shù)據(jù)的時間延時,另外一部分就是后續(xù)數(shù)字電路中的延時。延時的具體計算過程如下:數(shù)據(jù)傳輸時使用的時鐘信號是對總線時鐘的2分頻,當DSP的主頻是60 MHz時,總線時鐘頻率是30MHz,對它進行2分頻,可以計算出SCLK的周期是66.6ns(實際所測出的周期是78.2 ns)。另外通過測試得到PWM電路的延時最長時間是23.6 ns,鎖存器的最大延時是7.6 ns,移位寄存器的最大延時是3.O ns。由上述對CPLD數(shù)字電路的延時和對SCLK周期的測試,就可以得到這樣一個結(jié)論:設PWM電路的延時時間為t1、鎖存器的延時時間為t2、移位寄存器的延時時間為t3、SCLK的時鐘周期是Tc,在SPI傳輸?shù)倪^程中,整個電路的延時t可以這樣計算:

由于數(shù)字電路傳輸中存在這樣的延時,所以在寫DSP程序時,需要加入一定的延時。此實驗中加入的延時是2μs,可以實現(xiàn)可靠傳輸。

評論