QDR SRAM與Spartan3 FPGA的接口設計

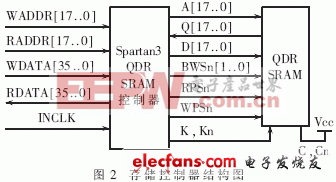

Spartan3系列FPGA是由Xilinx公司基于成功的Virtex-II FPGA架構而研發的性價比較高的一種產品。Spartan3器件有如下特點:嵌入式18×18乘法器支持高性能DSP應用;片上數字時鐘管理(DCM),無需外部時鐘管理器件;分布式的存儲器和SRL16移位寄存器邏輯能夠更高效執行DSP功能;18KB 塊RAM,可以用作緩存或是高速緩存;數字片上終端能夠消除對多個外部電阻器的需求;8個獨立的I/O陣列支持24種不同的I/O標準;Spartan3系列的FPGA獨有的特性可以簡化存儲控制器的設計。圖2是用Spartan3系列FPGA實現的存儲控制器結構圖。

該存儲控制器的設計可以在深度擴展模式下實現對四個SRAM的控制。每個QDR SRAM會收到對各自的讀寫端口進行控制的相互獨立的控制信號,而對所有的SRAM來說,地址和數據端口是共用的。

存儲控制器是以QDR SRAM工作在單時鐘模式下對其進行控制的,從而可以簡化存儲器接口。控制器工作在100MHz的時鐘頻率下,允許7.2Gbps的帶寬。存儲控制器有獨立的讀寫狀態機,存儲控制器的控制是基于兩位指令輸入的形式來實現的。

2.2 QDR SRAM和Xilinx Spartan3系列FPGA的接口連接

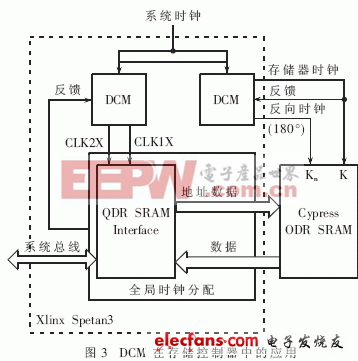

Spartan3系列的FPGA獨有的特性可以簡化存儲控制器的設計。Spartan3系列產品是業界成本最低的可編程邏輯電路。在Spartan3系列FPGA中,有DCM(數字時鐘管理)模塊,可以用來消除內部全局時鐘網絡的時鐘歪斜,或者消除為片外其他系統組成部分提供時鐘的過程中所出現的時鐘歪斜。DCM中的DLL能夠使控制器完成FPGA的片上時鐘和QDR SRAM之間的零時鐘歪斜。除此之外,DCM還提供其他的功能,如相位調解,分頻和倍頻。圖3所示為DCM在存儲控制器設計中的應用。

評論