MSK信號檢測識別的FPGA實現(xiàn)

2.2 高速STFT 實現(xiàn)

為了覆蓋整個跳頻帶寬,中頻信號的采樣率設為700MHz, 而FPGA 無法直接處理這樣高速率的數(shù)據(jù),因此需要采用多路并行處理,即將中頻采樣信號分成4 路,每路175 MHz, 這使得在FPGA 中運算成為可能。相應的FFT運算也需要多個運算模塊并行處理,這樣的代價便是增加了硬件資源消耗。數(shù)據(jù)接收及FFT處理的實現(xiàn)框圖如圖2 所示。

要實現(xiàn)50%的數(shù)據(jù)重疊處理,需要2 個圖2 所示的模塊,這樣粗測頻引導模塊就需要8 個1 024 點FFT運算單元,在FPGA 中使用FFT的IP 核實現(xiàn)。

完成FFT處理后需要進行幅度譜計算和譜峰提取,通過對譜峰的能量檢測進行是否存在信號的判斷,并根據(jù)譜峰位置得到粗測頻結果,以此引導正交下變頻模塊。2.3 數(shù)字正交下變頻的實現(xiàn)

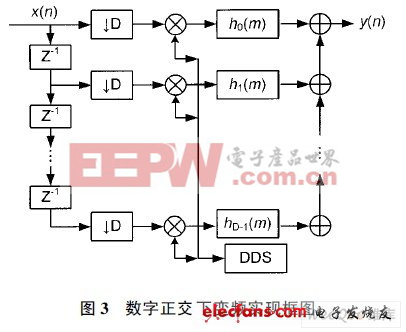

數(shù)字正交下變頻模塊根據(jù)前面得到的引導信息,設置合適的數(shù)字本振頻率值,將信號搬移到零中頻,并對信號進行低通濾波和抽取,得到低采樣率的零中頻數(shù)據(jù),以方便后續(xù)處理。數(shù)字正交下變頻采用基于多相抽取濾波器的多路并行結構,實現(xiàn)如圖3所示。

2.4 信號識別的實現(xiàn)

信號識別的主要模塊是平方運算和信號的幅度譜分析。為了體現(xiàn)MSK 信號的特征,對經(jīng)過正交下變頻得到的數(shù)據(jù)進行平方運算。如果直接對數(shù)據(jù)進行常規(guī)的平方處理,結果會產(chǎn)生零頻分量,對后續(xù)處理造成不利影響。為了消除這種影響,需要將正交的復數(shù)據(jù)進行坐標變換,轉變成幅度和相位的表示形式。這樣再進行平方運算時,保持幅度值不變,相位值變成原來的2 倍并經(jīng)過相位解卷繞處理,最后再經(jīng)過坐標反變換,得到經(jīng)過平方運算的復數(shù)據(jù)。

坐標變換可采用計算器(CORDIC) 運算IP 核實現(xiàn),有利于節(jié)省硬件資源,提高運算效率。

幅度譜分析模塊通過粗測頻引導確定信號到來,對經(jīng)過平方運算的零中頻數(shù)據(jù)進行FFT處理,得到信號的幅度譜。進行譜分析時按照如下步驟:

① 提取過檢測門限的譜峰點;

② 確定最大譜峰的位置;

③ 確定距離最大譜峰位置左右5 MHz 處是否存在與最大譜峰值相差不大的譜峰;

④ 檢測2 個譜峰連線的中點位置是否是2 倍的有效信道載頻頻點。

3 試驗結果

為了驗證算法實現(xiàn)是否能正確截獲并識別MSK 目標信號,使用泰克公司的任意信號發(fā)生器

信號發(fā)生器又稱信號源或振蕩器,它是指產(chǎn)生所需參數(shù)的電測試信號的儀器。在生產(chǎn)實踐和科技領域中有著廣泛的應用。按信號波形可分為正弦信號、函數(shù)(波形)信號、脈沖信號和隨機信號發(fā)生器等四大類。各種波形曲線均可以用三角函數(shù)方程式來表示。常見的有函數(shù)信號發(fā)生器。

AWG7122B 模擬產(chǎn)生了目標信號環(huán)境,并使用硬件平臺進行了接收測試

,為了便于觀察計算結果,使用Xilinx 公司的在線邏輯分析儀軟件ChipScope 截取了FPGA 內(nèi)部的運算數(shù)據(jù)和結果。

使用任意信號發(fā)生共設置了3 個信號,

信號1參數(shù)如下:

信號形式: 脈沖;

信號時長: * s;

信號間隔: 13 s;

脈內(nèi)調制:MSK;

碼元速率: 5 MHz;

信號2 的參數(shù)如下:

信號形式: 單頻脈沖;

信號時長: 5 s;

信號間隔: 50 s;

信號3 的參數(shù)如下:

信號形式: 脈沖;

信號時長: 8 s;

評論