基于PCIE/104總線的高速數據接口設計

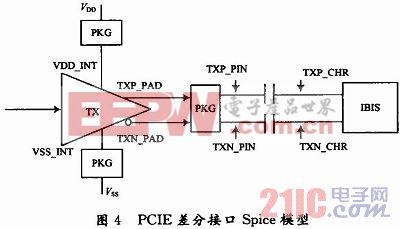

經過ploar軟件計算,將以上的數據輸入進去,再加入PCB廠家提供的介電常數等參數,最后得出的阻抗完全滿足設計需求。多層板的高速信號設計很有必要進行信號完整性仿真,應用廠家提供的IBIS模型,采用Hyperlynx對板子進行了本地端和時鐘端的信號完整性仿真。并根據仿真對布線提供了約束條件。而針對PCIE的高速差分端總線,因為在高速信號仿真方面IBIS模型還不夠精確,所以,PLX公司對其兩對收發端口提供SPice模型,如圖4所示。本文引用地址:http://www.104case.com/article/150347.htm

將上訴模型導入HSpice中,同時引入PCIESwitch芯片給出的IBIS模型與板子上面的差分線trace的rglc模型。輸出端的仿真效果圖如下,可以看出差分信號的幅值是可以滿足PCIE規范的電氣要求的。

3 結語

PC/104作為一種嵌入式總線標準已經被很多控制系統所采用,而PCIE/104接口的提出將未來最為流行的串行差分總線結構,引入到了這種嵌入式總線標準,從而為各種高速、高帶寬的嵌入式系統提供了選擇。目前該系統由于采用了PCIE總線,相比采用PLX9054實現的PCI接口具有明顯的優勢。

評論