基于PCIE/104總線的高速數據接口設計

摘要:PC/104作為一種工業嵌入式的總線標準,由于其小尺寸結構、低功耗,以及軟件通用性而被廣泛用于航空航天、工業控制等領域。這里主要介紹了下一代總線技術PCIE總線在PC/104標準下的應用。闡述了數據接口卡的系統組成和各單元的功能,以及驅動在linux操作系統下的實現原理。自行設計并實現了板卡原理圖和PCB,同時簡述了高速PCB仿真方面的知識,并針對PCIE差分線進行了版級仿真。最后利用PLX公司提供的開發套件在Linux操作系統下完成了板卡驅動的開發和調試。

關鍵詞:PCIe總線;PC/104;嵌入式;PCB仿真

0 引言

PCIE總線是由Intel公司提出用來取代現行PCI總線的下一代總線技術,被公認為未來總線的發展方向,目前已經成功應用在了商業機上。相對于目前流行的PCI總線,它具有如下特點:

采用了串行點對點模式,數據總線從并行走回向串行無疑是一個趨勢,如現在流行的SATA總線、PCIE總線和rapidIO總線都是串行總線。現在串行總線在速度上的優勢可以說是毋庸置疑的。PCIE總線在每個方向上都有X1,X2,X4,X8,X16或X32個信號對,用戶可根據不同的需求采用不同的配置。同時串行信號還具有管教更少,便于調試的優點。

PCIE采用了基于數據包的協議來編碼事物,而不是PCI體系結構的總線周期。數據包被串行發送和接受,并被字節拆分來通過物理鏈路。鏈路上實現的通道越多,數據包發送的數據越快,鏈路的帶寬也越寬。同時PCIE還定義了各種類型的數據包,如存儲器讀/寫請求、I/O讀/寫請求、配置讀/寫請求、消息請求和完成數據包等。

PC/104標準是一種嵌入式的總線標準,具有功耗低,尺寸小,堆棧式結構的特點。隨著目前各種應用數據傳輸量的增大,現行的PCI總線在帶寬方面已經略顯疲態,而新近瑞士邏輯提出的PC/104 Express標準,使得PCIE總線技術被成功地應用在了PC/104標準的板卡上。本文采用了PLX公司的PEX8311橋接芯片,完成了PCIE到局部總線接口的轉換,應用PLX公司提供的開發工具在Linux操作系統下實現了板卡的驅動應用。在軟硬件兩方面進行了設計,完成了PCIE/104板卡的功能,升級了系統的總線。

1 PCIE/104高速信號接口卡的系統

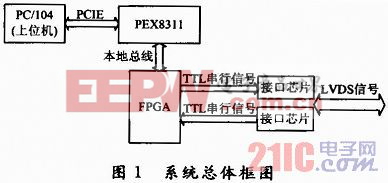

PCIE/104高速信號接口卡的系統設計方案如圖1所示。

外部傳感器采集到的數據通過LVDS,RS 422等電平方式,以固定的不同串口波特率傳到FPGA內部集成的各自對應的雙口RAM中。當寫入了固定字節后,設定標志位stage為1,同時發出中斷信號LINT#給PEX8311。PEX8311產生了assert_INT1信息,并通過PCIE接口發給上位機。上位機保存好現在的任務后,通過PCIE開始發出存儲器讀命令給PEX8311。PEX8311獲得命令后,向FPGA發出本地總線申請信號,FPGA作為本地端的控制器將本地總線控制權交給PEX8311。PEX8311開始讀數據,首先要進行的是讀取標志位,在讀取了標志位后,上位機就知道是哪幾路串口信號需要讀入。然后,把標志位清掉,這樣相當于清掉了中斷信號。接著,中斷服務程序在進入到各個串口的RAM中,來讀取相應的數據。在多路串口信號傳輸過來時,針對該系統,采用的是優先滿足高速串口的原則,也就是采用高速串口的標志位作為中斷信號,每次產生中斷后查詢其他標志位。數據到上位機后待處理。該系統目前實現的是兩路串口,而多路串口原理相同。

評論