基于CY7C68013A和FPGA的ADSP-TS101擴展USB接口設計

Link口協議的一大特點就是在收發數據時可以選擇是否需要校驗位VERE比特,VERE的啟用或關閉可以通過ADSP-TS101中的寄存器來設置,也可以通過FPGA模塊中的Verein信號置高或置低來設置。該設計在FPGA中設置VERE信號的啟用或關閉。當VERE啟用后,FPGA模塊中的輸出信號Rx_Vere_Bad用于表征最后接收的128 b數據是否正確。由于使用VERE有兩個好處,一是能保證數據的完整性;二是能減小在兩個時鐘不嚴格一致的系統中傳輸數據時產生數據重疊的可能性。因而在設計中采用了帶數據校驗的傳輸方式。3 USB傳輸設計

3.1 傳輸方式的確定

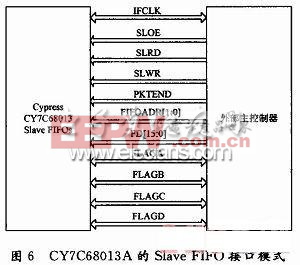

CY7C68013A芯片具有GPIF模式和從屬FIFO(Slave FIFO)模式兩種接口工作模式。在本設計中,USB數據傳輸存儲模塊負責完成存儲算法產生的大量數據的高速傳輸,由于不涉及到對外部電路的控制,所以不選用GPIF模式,而選擇Slave FIFO模式進行連接。在數據傳輸時,用Slave FIFO接口模式,批量傳輸,自動輸入(AUTOIN)方式,使用EP6端口作為上行輸入緩沖區。CY7C68013A的,Slave FIFO接口模式如圖6所示。

3.2 EZ-USB FX2時序設計

在本設計的FPGA中,設計了如圖6的外部主控制器的功能邏輯。由于DSP端Linkport口數據傳輸速率很高,而在USB端的速率可能無法跟Linkport口的數據率相匹配,故在FPGA中開辟一個2KB的FIFO,經由Linkport上傳的數據首先傳送到FIFO中,之后再經由USB口上傳至主機。為了保證數據傳輸的完整性,設計USB的數據傳輸速率為DSP Link口的1/8。在此,對FPGA邏輯應用Modelsim軟件進行了仿真,仿真結果如圖7所示。

圖7中,在LxCLKIN時鐘的上升沿和下降沿將DSP_Data中的數據寫入到FPGA的FIFO中,然后再把FIFO中的數據從數據線USB_Data中輸出給EZ-USB FX2的FD數據線,最后經由USB傳送給主機。圖中USB_Data的數據率明顯只有DSP_Data數據率的1/8,是符合設計要求的。

在上傳傳輸時,采用異步自動輸入方式。EZ-USB FX2芯片FIFO異步寫時序如圖8所示。根據此時序,在本設計中,FPGA輸出的USB_Data信號提供給USB的FD數據線,FPGA輸出的USB_SLWR提供給USB的SLWR,USB端便能在SLWR的下降沿把數據線FD中的數據寫入到FX2芯片FIFO中,并由USB傳送給主機。

4 結語

本文重點對DSP擴展USB接口的數據上行通道的硬件設計進行了詳細論述。本系統經測試驗證,通過該擴展USB接口,配合定制的上位機軟件,DSP數據上傳PC機的速率平均達到8 MB/s以上,連接可靠穩定,滿足對DSP變量實時監測的數據率需求,同時可通過此接口完成程序的加載與燒寫功能。僅需一臺帶USB接口的PC機,就能完成彈載DSP系統的實時測試與在線程序加載,簡捷、通用、方便,具有顯著的工程實用價值。

評論