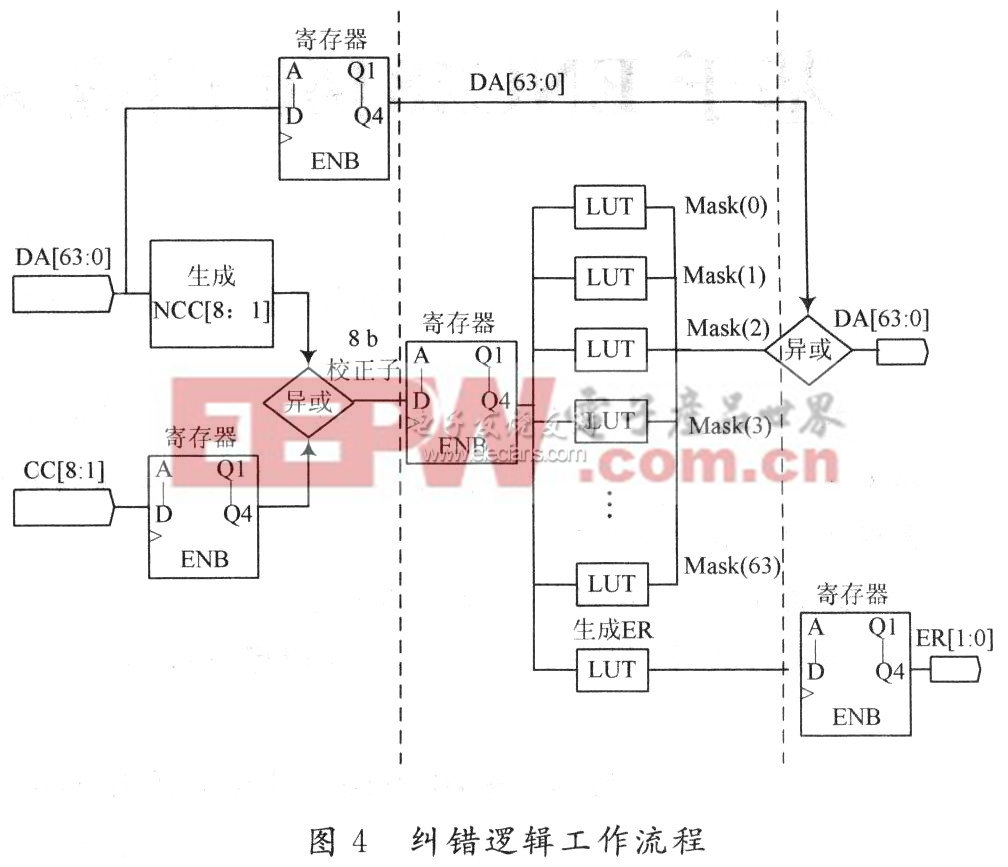

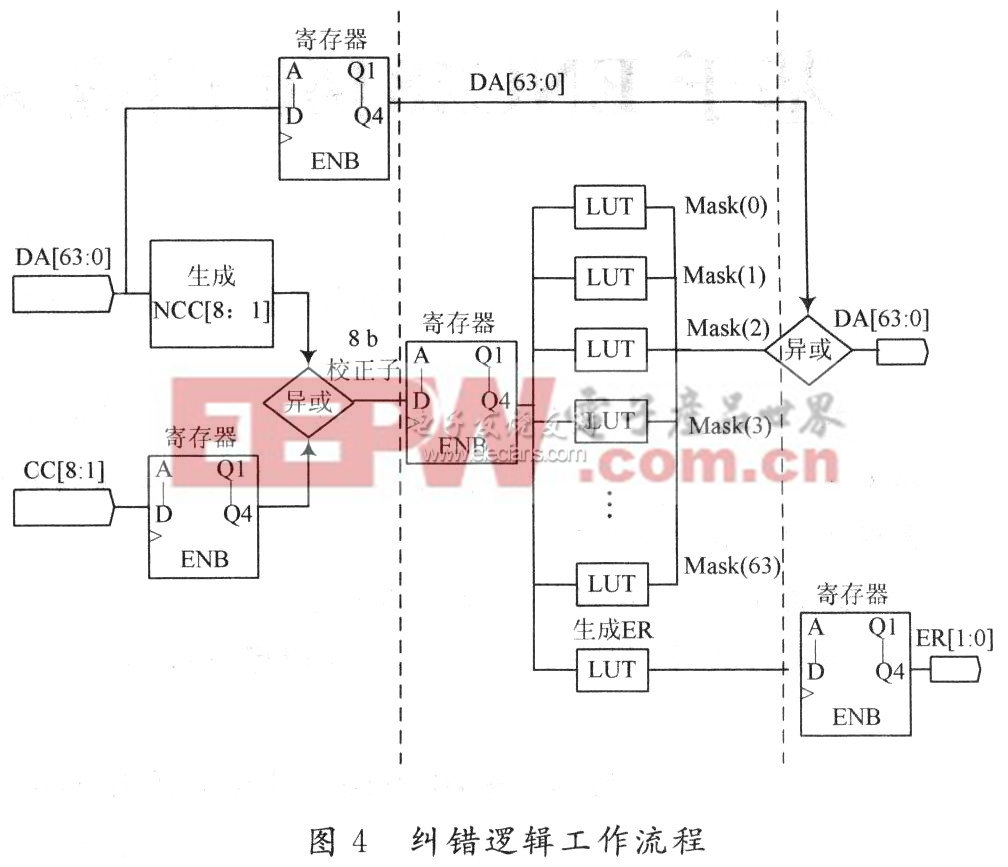

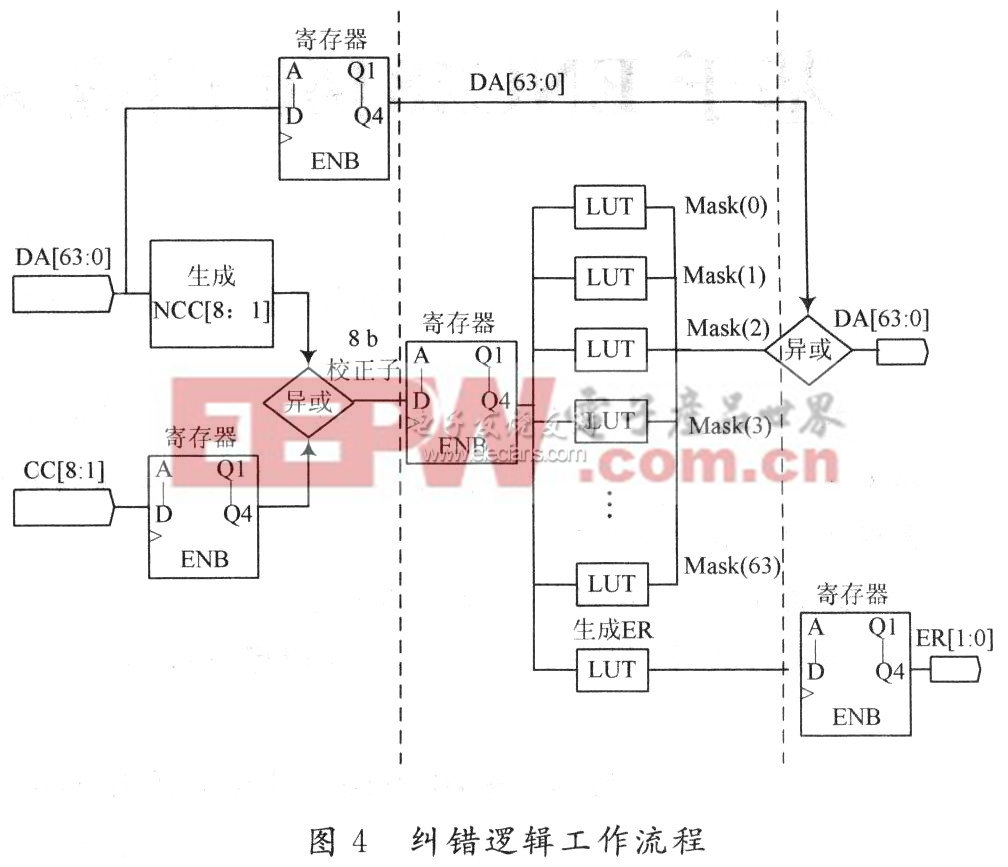

FPGA的檢糾錯邏輯設計采用VHDL語言實現。設計使主存儲器SRAMl中的64位數據新生成的NCC[7:0]與SRAM2中的7位校驗位CC[7:0]一起經過異或運算,生成8位的校正子,其中前7位就對應于前述定位錯誤數據的行號和列號的值,第8位用于判斷是否出現雙位元錯誤。8位校驗子的值可以求出1個64位糾錯掩碼(Mask),用以校正單位元錯誤。如果未檢測到錯誤,此掩碼的所有位都為零。如果檢測到單位元錯誤,相應掩碼會屏蔽除錯誤位之外的所有位。下一階段,使用原始數據對此掩碼進行異或運算。最終,錯誤位被反轉(或校正)至正確狀態。如果檢測到雙位元錯誤,所有掩碼位也都為零。使用1個雙位的數組(ER[1,O])用于報告檢測的錯誤類型(“OO”表示無錯、“01”表示單位元錯誤、“10”表示雙位錯誤、“11”表示無法判斷的多位錯誤)。整個糾錯邏輯的工作過程如圖4所示。生成錯誤類型報告數組和相應的校正掩碼的工作都在同一時鐘周期內完成,體現了采用FPGA進行并行處理的獨特優勢。本文引用地址:http://www.104case.com/article/150201.htm

3 結 語

對綜合后進行仿真的結果進行分析,期間人為地加入1位、2位、3位隨機分布的數據位錯誤,該系統能夠在2個系統時鐘周期內對1位錯誤的情況成功地檢測并予以糾正;對2位和3位錯誤情況也都進行了正確的類別判定。仿真結果表明,設計的系統比較理想,能滿足設計要求。

評論