基于FPGA的UART接口模塊設計

UART接口模塊由接收控制進程、讀數據進程、接收數據串/并轉換進程、狀態操作進程等進程構成。

在接收控制進程中同樣聲明了一個6比特的變量scir_v,由它的取值(狀態機)狀態來控制整個接收過程。其控制過程同發送模塊相似,這里不再贅述。下面給出的是接收數據進程的源代碼:

----接收行數據的串/轉換進程---

PROCESS(clk,reset)

BEGIN

IF(reset=0')'THEN

d_fb=00000000;

ELSIF(clkE'VENTANDclk=0')'THEN

IF((sh_r>=1000)AND(sh_r=

1111)AND(sl_r=01))THEN

d_fb(7)=rxd;

FORiIN0TO6LOOP

d_fb(i)=d_fb(i+1);--d_fb(0)被移

出;d_fb(7)被移空

ENDLOOP;

ENDIF;

ENDIF;

ENDPROCESS;

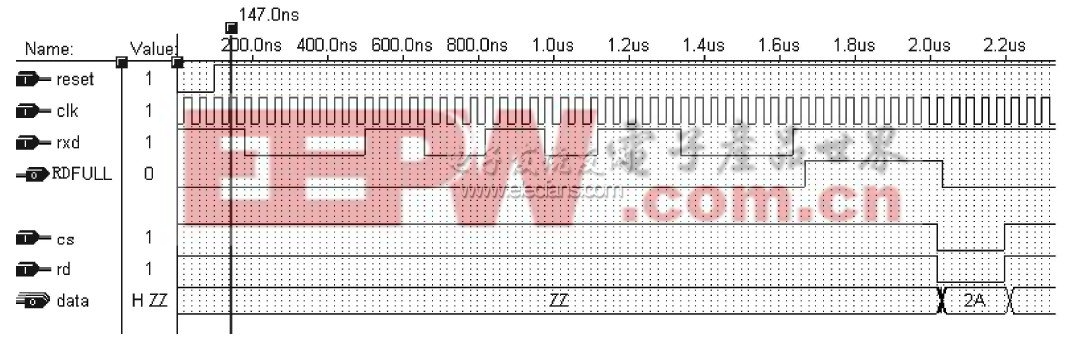

圖4給出的是接收數據的仿真圖。當rxd出現低電平后便啟動一次接收過程,當8比特的數據接收完畢后,rxd變為高電平,同時將RDFULL信號置為高電平有效,RDFULL有效表示接收寄存器已經存儲了一個剛剛接收到的數據,當CS和RD有效時將數據(實際接收到的數據是2AH)讀出,同時RDFULL被置成無效狀態。

圖4 接收數據的仿真波形

2.3 波特率發生器模塊

波特率發生器實際是一個分頻器,分頻器的輸出連接到SCI的CLK輸入端,且應為實際波特率的4倍頻。因為在發送和接收控制進程中,狀態機由一個6比特的寄存器(cit_v、cir_v)的高4位(sh_r、sh_t)進行控制,而高4位的狀態改變需要4個CLK時鐘(低2位向高4位進位)。當SCI與SCI進行通信時,通信雙方波特率選擇一致即可,當SCI同MCU通信時,SCI的波特率選擇同MCU定時器的溢出率即可,當SCI需要同PC通信時,才將SCI的波特率定制成:1.2Kbps,2.4Kbps,4.8Kbps直到115.2Kbps,這時要求SCI的晶體振蕩頻率要足夠高來滿足波特率的匹配,或采用(11.0592或22.1184MHz)的特殊晶體來滿足特率的匹配要求。

3 結論

將SCI下載到EPF10K10芯片中,40MHz有源晶振沒有進行分頻直接驅動SCI模塊,用ICL57176進行RS485轉換,用100m的網線進行了SCI與SCI之間全雙工通信。測試結果表明波特率達到10Mbps時通信是正確的

評論