基于FPGA的信號發生器設計

4 D/A 轉換器的連接

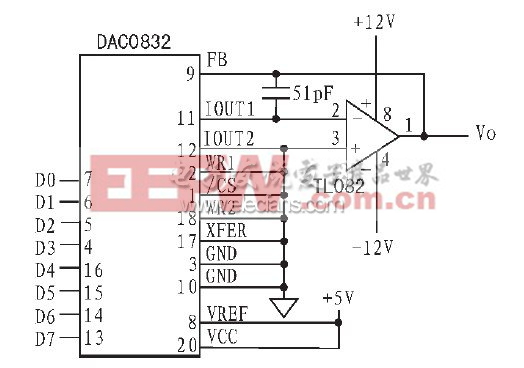

選擇一個D/A 轉換器,將數據選擇器的輸出與D/A 轉換器的輸入端連接。D/A 轉換器的可選范圍很寬,這里以常用的DAC0832 為例。DAC0832 的連接電路如圖6 所示。

圖6 DAC0832 的連接電路

5 實現與測試

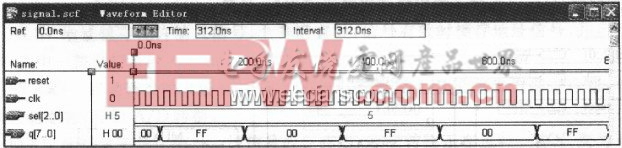

信號發生器頂層電路的仿真波形如圖7 所示,這里只就輸入選擇信號等于5 時的情況進行仿真,此時輸出波形是方波,輸出的數字信號為周期性的全0 或全1。

圖7 信號發生器頂層電路的仿真波形

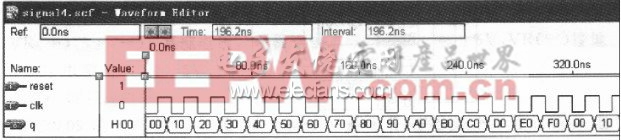

信號發生器的底層電路模塊也可以分別進行仿真,例如對階梯波信號產生模塊signal4 進行仿真,仿真波形如圖8 所示,輸出的數字信號為階梯狀變化。

圖8 階梯波信號產生模塊signal4 的仿真波形

6 結束語

硬件電路設計主要是設計相關模塊的設計思想的可視化,是相關模塊的電路圖的匯總和其相關仿真波形的集錦,該部分條理清晰,思路明確,從中我們可以清晰地看到該設計方案的具體模塊和整個設計的原理結構實圖;程序設計這一部分主要闡述該設計的設計方法與設計思想,進一步從軟件設計上揭示設計構思,主要包含了整個設計所用到的模塊的硬件描述語言的設計, 本文設計思路清晰,通過QuartusII 軟件進行波形仿真成功,特別是正弦信號發生器的LPM 定制對于編程不是特別強的人員提供另一種途徑來實現,加深理解EDA 的層次設計思想,很好的把握住了教學的改革方向,更好的鍛煉了學生理論聯系實踐的能力。

評論