基于FPGA的信號發生器設計

打開Mega Wizard Plug_In Manager 初始對話框, 選擇Create a new custom… 項。單擊Next 按鈕后,選擇Storage 項下的LPM_ROM, 再選擇ACEX1K 器件和VHDL 語言方式;最后輸入ROM 文件存放的路徑和文件名:F:sing_gntdata_rom (定制的ROM 元件文件名),單擊Next 按鈕,選擇ROM 控制線、地址線和數據線。這里選擇地址線位寬和ROM 中數據數分別為6 和64; 選擇地址鎖存控制信號inclock。

對于地址信號發生器的設計。方法一:用VHDL 語言設計6 位計數器,產生其元件符號;方法二:仍采用LPM 定制的方法。

1.3 完成頂層設計

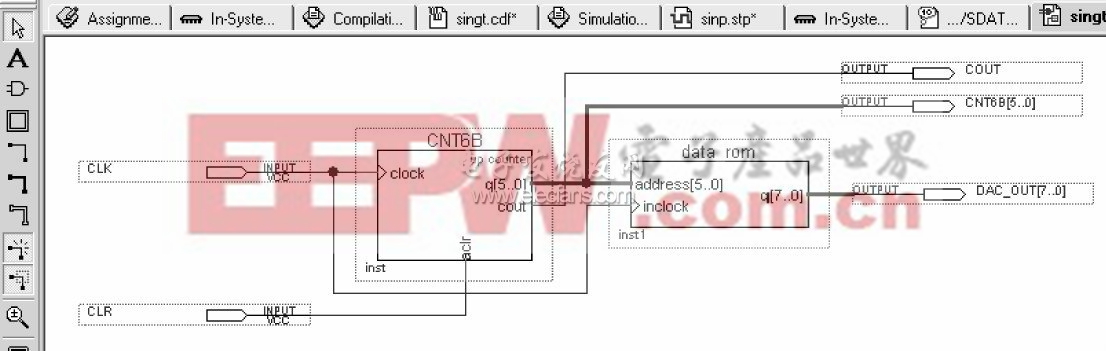

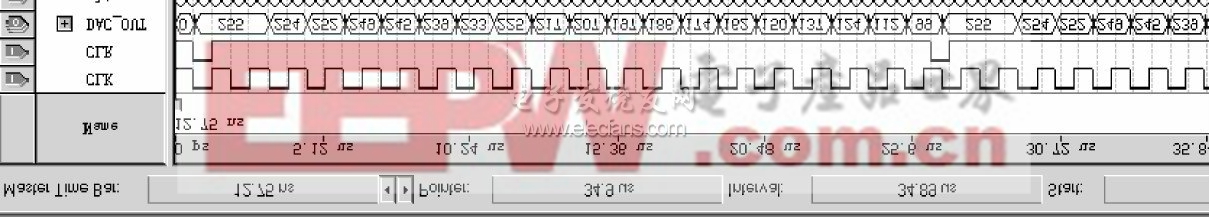

按圖3 畫出頂層原理圖,然后進行編譯,波形仿真如圖4所示。

圖3 簡易正弦信號發生器頂層電路設計

圖4 當前工程仿真波形輸出

對當前設計通過執行Quartus II 的命令Create ∠ Update/ Create Symbol Files for Current File,可以為設計電路建立一個元件符號,以便被頂層設計多功能信號發生器所調用。

2 其他信號部分原程序

其他各信號發生器可參照正弦信號發生器的設計方法設計或直接采用VHDL 硬件描述語言進行設計。

LIBRARY IEEE;--遞增鋸齒波的設計

USE IEEE.STD LOGIC 1164.ALL;

USE IEEE.STD LOGIC UNSIGNED.ALL;

ENTITY signal2 IS --遞增鋸齒波signal1

PORT(clk,reset:IN std_logic;--復位信號reset, 時鐘信號clk

q:OUT std_logic_vector (7 DOWNTO 0));--輸出信號q

END signal2;

ARCHITECTURE b OF signal2 IS

BEGIN

PROCESS(clk,reset)

VARIABLE tmp:std_logic_vector(7 DOWNTO 0);

BEGIN

IF reset='0' THEN

tmp:=00000000;

ELSIT rising_ege(clk)THEN

IF tmp=11111111THEN

tmp:=00000000;

ELSE

tmp:=tmp+1; --遞增信號的變化

END IF;

END IF;

q=tmp:

END PROCESS;

END b;

LIBRARY IEEE;--方波的設計

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

entity signal5 is --方波signal5

PORT(clk,reset:in std_logic; --復位信號reset,時鐘信號clk

q:out std_logic_vector (7 DOWNTO 0)); --輸出信號q,8 位數字信號

END signal5;

ARCHITEECTURE a OF signal5 IS

SIGNAL; a:std_logic;

BEGIN

PROCESS(clk,reset)

YARIABLE tmp:std_logic_vector(7 downto 0);

BEQIN

IF reset='0' then

a='0';

elsif rising_edge(clk)THEN

IF tmp=11111111 THEN

tmp:=00000000;

ELSE

tmp:=tmp+1;

END IF;

if tmp=10000000 then

a='1';

else

a='0';

END IF;

END IF;

END PROCESS;

PROCESS(clk,a)

BEGIN

IF rising_edge(clk)THEN

IF a='1' THEN

q=11111111;

ELSE

q=00000000;

END IF;

END IF;

END PROCESS;

END a;

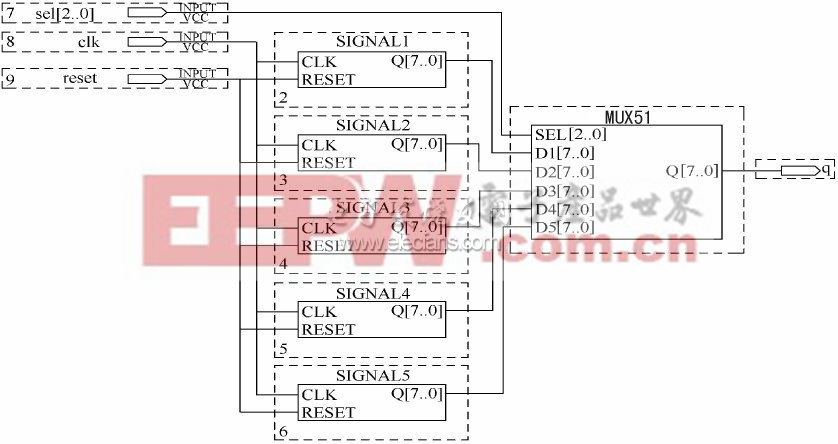

3 頂層電路的設計

將上述6 個模塊生成符號,供頂層電路調用。這些模塊分別是:遞減鋸齒波信號產生模塊signall、遞增鋸齒波信號產生模塊signal2、三角波信號產生模塊signal3、階梯波信號產生模塊signal4、方波信號產生模塊signal5 和數據選擇器mux51。頂層電路的連接如圖5 所示。

圖5 信號發生器頂層電路

評論