嵌入式微處理器IP core設計與分析

(1)控制器模塊的狀態機實現

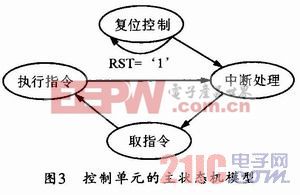

根據本文中多數輸出要保持一個完整的時鐘周期,此時鐘周期內輸出不能受時鐘信號的影響,所以采用Moore型有限狀態機來完成控制器模塊的設計。整個控制模塊的設計通過主狀態機和子狀態機兩步來完成。注狀態機模型如圖3所示。本文引用地址:http://www.104case.com/article/149766.htm

以中斷處理子狀態機設計為例,對子狀態機的設計進行說明,狀態轉換圖如圖4所示。

(2)存儲器模塊的設計

存儲器是數字系統的重要組成部分,數據處理單元的處理結果需要存儲,許多處理單元的初始化數據也需要存放在存儲器中。本文的存儲器結構,采用的是將程序存儲器和數據存儲器分開尋址的哈佛結構。同時又將數據存儲器分為內部數據存儲器和外部數據存儲器兩部分來設計。

(3)中斷系統設計

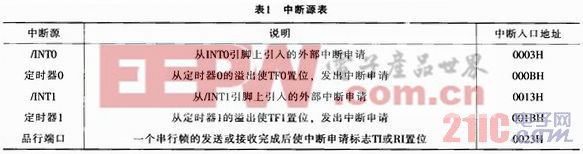

本文中的中斷系統在控制通路來完成,共提供了5個中斷源,同時通過對中斷優先級寄存器IP中的某位的置位或清除,可以把每個中斷源分別編程為高優先級或低優先級。如表1所示。

(4)定時器/計數器模塊的設計

定時器/計數器是微處理器中重要的外圍模塊,它主要是完成作為定時器和事件計數器的功能。在作為定時器工作時,每一個機器周期使定時寄存器加1計數。在作為事件計數器工作時,是對外部輸入負跳變信號做加法計數,規定在每個機器周期的某一狀態采樣此信號,在前一個周期采樣到“1”,后一個周期采樣到“0”時計數加1,而在檢測到跳變信號后的那個周期的下一個狀態時,新的計數值裝入計數寄存器。

3 系統綜合、仿真驗證與性能分析

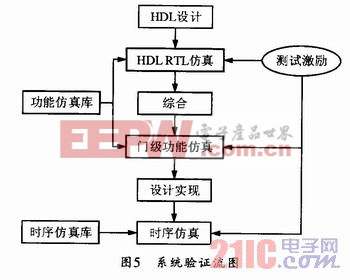

在整個微處理器IP核的設計過程中,利用可編程邏輯器件進行電路驗證對于保證設計的正確性和投片成功十分重要。在FPGA的設計流程中包括三種基本的驗證方法:HDL、RTL級描述仿真,門級仿真和布線后的時序仿真。具體驗證流程如圖5所示。仿真的目的就是要確認設計的正確性。如果出錯的話,則通過分析仿真器的輸出波形,找出出錯的原因,并對原設計進行修改。

評論