嵌入式微處理器IP core設(shè)計(jì)與分析

摘要:本文在對(duì)傳統(tǒng)微控制器進(jìn)行系統(tǒng)分析的基礎(chǔ)上,提出了一種較好的改進(jìn)設(shè)計(jì)方法。回避了傳統(tǒng)微控制器基于累加器的ALU結(jié)構(gòu)及算術(shù)邏輯指令:并在指令執(zhí)行時(shí)序上盡量減少指令執(zhí)行所需的時(shí)鐘周期。通過(guò)仿真驗(yàn)證證明該設(shè)計(jì)方法提高了指令的執(zhí)行效率和微控制器的運(yùn)行效率,同時(shí)避免了通常采用并行處理設(shè)計(jì)中多級(jí)流水線設(shè)計(jì)帶來(lái)的內(nèi)部復(fù)雜的控制邏輯設(shè)計(jì)。

關(guān)鍵字:微控制器;IP core;流水線

在嵌入式系統(tǒng)的設(shè)計(jì)中,IP技術(shù)為SoC的設(shè)計(jì)提供了有效途徑,是SoC的技術(shù)支撐。當(dāng)然,在國(guó)內(nèi)開發(fā)出具有自主知識(shí)產(chǎn)權(quán)的IP模塊還面臨著許多問(wèn)題,如核心算法的優(yōu)化、不同層次模塊的建立、模塊的可重用問(wèn)題以及IP模塊的標(biāo)準(zhǔn)化問(wèn)題等。對(duì)于嵌入式處理器IP核,面對(duì)的挑戰(zhàn)就是如何選擇一個(gè)滿足其應(yīng)用需求的處理器。現(xiàn)已有數(shù)百種嵌入式處理器,每組都具備一組不同的外設(shè)、存儲(chǔ)器、接口和性能特性,用戶很難做出一個(gè)合理的選擇。本文設(shè)計(jì)的微處理器的指令集與標(biāo)準(zhǔn)8051單片機(jī)完全兼容,這樣有利于開發(fā)人員的使用。

1 總體設(shè)計(jì)方案的擬定

1.1 提出改進(jìn)方案

首先在對(duì)典型八位微處理器進(jìn)行了詳盡地剖析的基礎(chǔ)上,指出在傳統(tǒng)典型微處理器內(nèi)核中制約微處理器整體性能的主要因素,然后提出以下改進(jìn)方案:

(1)微處理器的內(nèi)核結(jié)構(gòu)上,將乘、除法單元各自獨(dú)立出來(lái)來(lái)完成算術(shù)邏輯指令中的乘、除法運(yùn)算。這樣可以回避傳統(tǒng)典型微處理器基于累加器的ALU結(jié)構(gòu)及算術(shù)邏輯指令,從而提高邏輯指令的執(zhí)行效率。

(2)在指令系統(tǒng)上,通過(guò)采用類RISC的指令系統(tǒng)和硬布線直接產(chǎn)生控制信號(hào)的方式來(lái)簡(jiǎn)化指令譯碼器的設(shè)計(jì)。同時(shí)為內(nèi)核添加指令緩沖區(qū)、采用指令流水線技術(shù)、多管道并行執(zhí)行指令。

(3)指令時(shí)序上,設(shè)計(jì)中盡量減少指令執(zhí)行所需的時(shí)鐘周期,提高微處理器的運(yùn)行效率。

1.2 總體設(shè)計(jì)思路

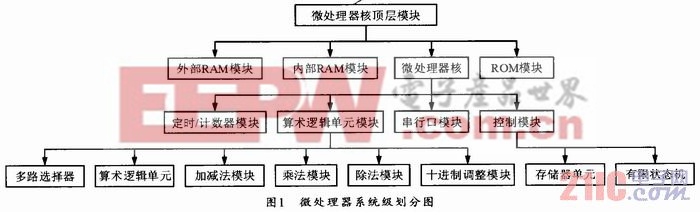

根據(jù)IP core通用的設(shè)計(jì)方法,本文采用了標(biāo)準(zhǔn)的自頂向下的設(shè)計(jì)方法。就是根據(jù)系統(tǒng)級(jí)的內(nèi)容,把系統(tǒng)劃分為單元,然后再把每個(gè)單元?jiǎng)澐譃橄乱粚哟蔚膯卧@樣一直劃分下去,直到最底層的單元可以用硬件描述語(yǔ)言進(jìn)行設(shè)計(jì),如圖1所示;接著在完成各個(gè)模塊設(shè)計(jì)的基礎(chǔ)上完成系統(tǒng)級(jí)設(shè)計(jì);然后進(jìn)行整個(gè)系統(tǒng)的仿真驗(yàn)證;最后選用特定的FPGA芯片進(jìn)行綜合、布局布線以及功能后仿真。

2 各子模塊的設(shè)計(jì)

2.1 ALU模塊

算術(shù)邏輯單元(ALU)是微控制器的核心部件,ALU的設(shè)計(jì)依賴于指令系統(tǒng),ALU采用什么樣的結(jié)構(gòu)、設(shè)置那些功能都是建立在對(duì)系統(tǒng)指令集分析的基礎(chǔ)上來(lái)完成。

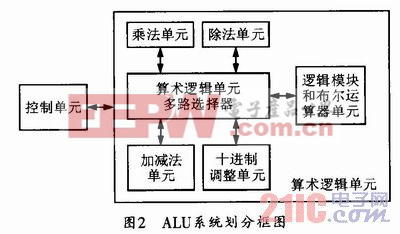

根據(jù)算術(shù)運(yùn)算類指令可知,ALU單元主要要完成的功能有:帶/不帶進(jìn)位加/減法、乘法、除法、十進(jìn)制調(diào)整、邏輯運(yùn)算以及布爾操作的實(shí)現(xiàn)。整個(gè)操作的完成是通過(guò)多路選擇器控制來(lái)完成。因此,我們可以對(duì)整個(gè)ALU系統(tǒng)進(jìn)行如圖2劃分,然后對(duì)各個(gè)子模塊進(jìn)行設(shè)計(jì)。

2.2 控制通路的設(shè)計(jì)

本文中的控制通路由譯碼器模塊和控制器模塊兩部分組成。這部分的設(shè)計(jì)是在對(duì)指令系統(tǒng)進(jìn)行正確分析的基礎(chǔ)上來(lái)完成。

設(shè)計(jì)控制通路有兩種主要的方法。微程序控制(或微序列控制)方式使用存儲(chǔ)器查表方式來(lái)輸出控制信號(hào),而硬連線控制使用時(shí)序邏輯和組合邏輯來(lái)產(chǎn)生控制信號(hào)。硬件直接實(shí)現(xiàn)的控制單元一般用有限狀態(tài)機(jī)實(shí)現(xiàn),通常有較高的運(yùn)算速度;但是通用性差,每個(gè)電路都必須專門設(shè)計(jì)控制單元。每一種方法都有一些變形形式。由于本文中微處理器的控制相對(duì)簡(jiǎn)單,所以在設(shè)計(jì)中采用了硬連線控制方法。

評(píng)論