基于USB設(shè)備控制器的端點(diǎn)緩沖區(qū)的優(yōu)化設(shè)計(jì)

對(duì)于USB的控制端點(diǎn),其接收的最大數(shù)據(jù)包為64 b。故本文設(shè)計(jì)的雙向FIFO使用的sram亦為64 b。使用memory complier生成。圖5是設(shè)計(jì)的雙向FIFO在Modelsim下的仿真波形圖。該波形顯示了方向0寫(xiě)數(shù)據(jù),方向1讀數(shù)據(jù)和方向1寫(xiě)數(shù)據(jù),方向0讀數(shù)據(jù)的過(guò)程。

2.2 其他端點(diǎn)的優(yōu)化設(shè)計(jì)

對(duì)于USB設(shè)備控制器的其他端點(diǎn),由于其與控制端點(diǎn)有所不同。控制端點(diǎn)是一個(gè)雙向端點(diǎn),而非控制端點(diǎn)單向的傳輸。故對(duì)于非控制端點(diǎn)對(duì)應(yīng)的緩沖區(qū)的容量設(shè)定,應(yīng)使USB的帶寬利用率盡量達(dá)到最高。由于USB規(guī)范中規(guī)定緩沖區(qū)必須有足夠的空間,可以為全(高)速設(shè)備容納一個(gè)時(shí)間片所能傳輸?shù)臄?shù)據(jù)量的兩倍的容量。這樣USB在處理一個(gè)數(shù)據(jù)分組的同時(shí),可以接收下一個(gè)數(shù)據(jù)分組。以此種重疊技術(shù)可以提高總線利用率。如果批量端點(diǎn)的緩沖區(qū)的深度設(shè)計(jì)為1 024 B。就可以得到最大的帶寬利用率。

圖6是其他端點(diǎn)所采用的雙緩沖FIFO方案示意圖。在狀態(tài)1,req0控制訪問(wèn)FIFO0,reql控制訪問(wèn)FIFO1;在狀態(tài)2,req0切換到訪問(wèn)FIFO1,req1切換到訪問(wèn)FIFO0。基于雙緩沖FIFO的設(shè)計(jì)方案可使其他端點(diǎn)的帶寬利用率達(dá)到最高,滿足高速傳輸?shù)男枨蟆?br />

3 電路的ASIC實(shí)現(xiàn)結(jié)果

對(duì)上述設(shè)計(jì)方案采用Verilog硬件描述語(yǔ)言進(jìn)行設(shè)計(jì)。仿真工具為Modelsim SE 6.2b,前仿真通過(guò)后,對(duì)設(shè)計(jì)好的電路使用Design Complier進(jìn)行綜合。綜合所使用的工藝庫(kù)是SMIC 0.18 μm工藝庫(kù)。

對(duì)于控制端點(diǎn),考慮到其主要處在SIE時(shí)鐘和MCU時(shí)鐘之間,對(duì)其所加的時(shí)鐘約束分別為60 MHz和30 MHz;此外還對(duì)傳統(tǒng)的雙緩沖FIFO結(jié)構(gòu)進(jìn)行了綜合,兩者所加約束完全一致。將兩者的電路的綜合結(jié)果對(duì)比如表2所示。

對(duì)比表2可知在保證控制端點(diǎn)功能的前提下,本文所采用的新型FIFO結(jié)構(gòu)比傳統(tǒng)雙FIFO結(jié)構(gòu)在電路的實(shí)現(xiàn)面積方面減小了45.3%。

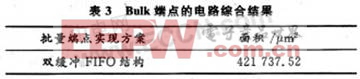

對(duì)于其他端點(diǎn)所采用的雙緩沖FIFO方案保證了傳輸速度,但卻是以犧牲面積為代價(jià)換來(lái)的。表3給出了批量(Bulk)傳輸端點(diǎn)(兩個(gè)深度為512 B的FIFO)的實(shí)現(xiàn)面積報(bào)告。

4 結(jié) 語(yǔ)

USB設(shè)備控制器端點(diǎn)緩沖區(qū)的性能,直接關(guān)系到總線的帶寬利用率。這里分析了USB的四種傳輸類(lèi)型并根據(jù)其特點(diǎn)靈活的設(shè)計(jì)了不同的方案,并給出了最終電路的ASIC實(shí)現(xiàn)結(jié)果。特別是針對(duì)控制端點(diǎn)所提出的一種新方案具有一定的通用性,該方案可以應(yīng)用在其他類(lèi)似場(chǎng)合的設(shè)計(jì)中。本文引用地址:http://www.104case.com/article/149541.htm

pid控制器相關(guān)文章:pid控制器原理

評(píng)論