基于FPGA的CAN總線通信節點設計

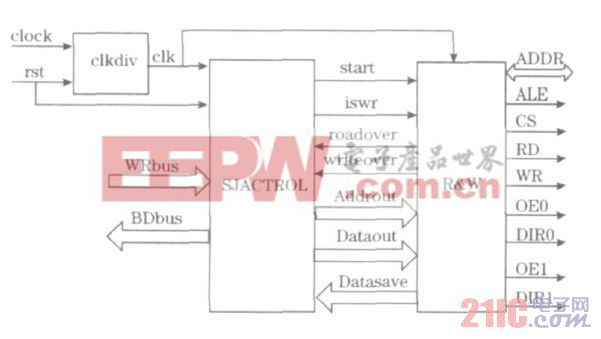

FPGA頂層的模塊設計如圖5所示。其中clkdiv模塊是將輸入的50MHz時鐘clock十分頻后作為模塊基準時鐘。SJACTROL模塊是控制總線通信的主模塊,而RW模塊則是根據主模塊的信號生成SJA1000所需要的讀寫時序信號。SJACTROL模塊通過start和iswr兩個信號通知RW模塊是否要進行讀或寫總線操作。若是寫操作,則將地址和數據通過Addrout和Dataout傳遞給RW,RW將負責把數據準確地送到SJA1000的數據地址復用總線ADDR,并驅動SJA1000接收數據,在寫操作完成后發送writeover信號通知SJACTROL寫操作完成。讀操作時RW根據SJACTOL送來的地址,從SJA1000的數據總線上讀取數據,并將得到的數據通過Datasave總線返回給SJACTROL。

圖5頂層模塊設計

SJACTROL的狀態機通過5個狀態的轉換來實現控制:空閑狀態、初始化狀態、查詢狀態、讀狀態、寫狀態。RW則是按照SJA1000的芯片數據手冊進行時序邏輯設計。在編寫模塊時,需注意雙向總線的編寫技巧。雙向口最好在頂層定義,否則模塊綜合的時候容易出錯。

3仿真結果

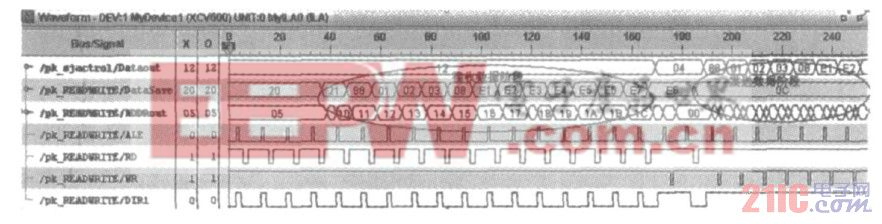

FPGA中利用Verilog編程產生SJA1000的片選信號CS,地址鎖存信號ALE,讀寫信號RD、WR。這些控制信號共同驅動SJA1000進行數據接收和發送。設計選取的是virtex系列的芯片,邏輯開發在ISE平臺上進行。在FPGA的調試階段,使用xilinx的應用軟件ChipScopepro(在線邏輯分析儀)來在線觀察FPGA設計內部信號的波形,它比傳統的邏輯分析儀更方便。圖6為在線進行數據傳送接收時的實際波形。

圖6SJA1000接收和發送數據的時序仿真

4結束語

通過對CAN通信系統的分析,利用FPGA作為CAN通信節點的主控制單元,對CAN節點的硬件接口電路設計方案進行了詳細的說明,并編寫了CAN節點通信流程中的初始化程序、數據發送接收程序。通過軟硬件的聯調,實現了CAN總線的通信功能,系統工作狀態良好。實踐證明CAN通信節點采用FPGA作為核心控制單元,與傳統的單片機設計相比,更加靈活并且擴展性更強。

評論