采用Xilinx 和FPGA的DDR2 SDRAM存儲器接口控制器的設計

用于地址、控制和數據的物理層接口在 I/O 模塊 (IOB) 中實現。讀數據在鎖存器的第二級(也是 IOB 的一部分)重新采集。本文引用地址:http://www.104case.com/article/148961.htm

Virtex-4 和 Virtex-5 FPGA 存儲器接口參考設計支持兩種讀數據采集技術。Virtex-4FPGA 支持的直接時鐘技術延遲了讀數據,因而使用 IOB 的輸入 DDR 觸發器中的系統時鐘可直接寄存讀數據。為將 FPGA 時鐘對齊到最佳狀態,對每個讀數據位都會單獨進行校驗。這種技術為高達 240 MHz 的時鐘速率提供了足夠的性能。

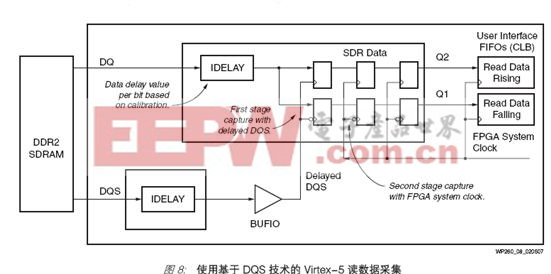

第二種技術稱為基于 DQS 的技術。此技術用于更高的時鐘速率,Virtex-4 和 Virtex-5FPGA 二者都支持此技術。它使用存儲器 DQS 來采集相應的讀數據,數據被此 DQS的延遲信號(通過一個局部 I/O 時鐘緩沖器 (BUFIO) 分配)寄存。此數據然后在觸發器的第二級與系統的時鐘域同步。IOB 中的輸入串行器/ 解串器功能用于讀數據采集;第一對觸發器把數據從延遲的 DQS 域中傳輸到系統的時鐘域(圖8)。

兩種技術都涉及到 tap 延遲 (IDELAY) 單元的應用, 在由校驗邏輯實現的校驗程序中,這些延遲單元會有所變化。在系統初始化期間,會執行此校準程序以設置 DQS、數據和系統時鐘之間的最佳相位。這樣做的目的是使時序余量最大化。校準會消除任何由過程相關的延遲所導致的不確定性,從而補償對于任何一塊電路板都不變的那些通路延遲成分。這些成分包括 PCB 跡線延遲、封裝延遲和過程相關的傳播延遲成分(存儲器和 FPGA 中都有),以及 FPGA I/O 模塊中采集觸發器的建立/ 保持時間。有的延遲是由系統初始化階段的過程、電壓和溫度所決定的,校準即負責解決這些延遲的變動。

在校準過程中會增加 DQS 和數據的延遲 tap 以執行邊沿檢測,檢測方式是通過連續從存儲器中讀回數據并對預編寫培訓模式或存儲器 DQS 本身進行采樣,直到確定數據選通脈沖 (DQS) 的前沿或前后兩沿。之后數據或 DQS 的 tap 數被設定,以提供最大的時序余量。對“基于 DQS”的采集而言,DQS 和數據可以有不同的 tap 延遲值,因為同步實質上分為兩個階段:一個先在 DQS 域中采集數據,另一個把此數據傳輸到系統時鐘域。

在更高的時鐘頻率下,“基于 DQS ”的采集方法就變得十分必要,其二階段方法能提供更好的采集時序余量,因為 DDR 時序的不確定性主要限于 IOB 中觸發器的第一級。此外,因為使用 DQS 來寄存數據,與時鐘-數據 (Tac) 變化相比較, DQS -數據變化的時序不確定性要小一些。例如,對于 DDR2 而言,這些不確定性就是由器件的tDQSQ 和 tQHS 參數給出的。

正如 Spartan-3 系列 FPGA 中所實現的那樣,Virtex-4 和 Virtex-5 FPGA 的寫時序由DCM 所支持,此 DCM 生成系統時鐘的兩相輸出。存儲器的 DQS 由一個輸出 DDR 寄存器來輸出,這個 DDR 寄存器由系統時鐘的同相時鐘驅動。寫數據則由超前系統時鐘90° 的一個 DCM 時鐘輸出進行時鐘控制。這種技術確保了在 FPGA 的輸出部分,DQS 與寫操作的數據中心對齊。

此設計的其他方面包括整體控制器狀態機的邏輯生成和用戶接口。為了使設計人員更容易完成整個設計,Xilinx 開發了存儲器接口生成器 (MIG) 工具。

控制器設計和集成

創建存儲器控制器是一項極其復雜、精細的任務,FPGA 設計人員要解決面臨的一道道難題,就需要 FPGA 隨附的工具提供更新水平的集成支持。

為設計的完整性起見,對包括存儲器控制器狀態機在內的所有構建模塊加以集成,十分必要。控制器狀態機因存儲器架構和系統參數的不同而異。狀態機編碼也可以很復雜,它是多個變量的函數,例如:

架構(DDR、DDR2、QDR II、RLDRAM 等)

組 (bank) 數(存儲器器件之外或之內)

數據總線寬度

存儲器器件的寬度和深度

組和行存取算法

最后,數據與 DQS 比 (DQ/DQS) 這類參數會進一步增加設計的復雜性。控制器狀態機必須按正確順序發出命令,同時還要考慮存儲器器件的時序要求。

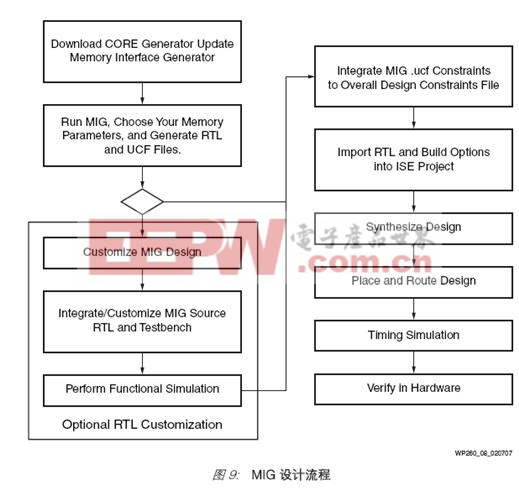

使用 MIG 軟件工具可生成完整的設計。該工具作為 CORE Generator 參考設計和知識產權套件的一部分,可從 Xilinx 免費獲取。MIG 設計流程(圖9)與傳統 FPGA 的設計流程非常相似。MIG 工具的優點是不必再為物理層接口或存儲器控制器從頭生成RTL 代碼。

MIG 圖形用戶界面 (GUI) 可用于設置系統和存儲器參數(圖10)。例如,選定 FPGA器件、封裝方式和速度級別之后,設計人員可選擇存儲器架構,并挑選實際存儲器器件或 DIMM。同是這一個 GUI,還可用于選擇總線寬度和時鐘頻率。同時,對于某些FPGA 器件,它還提供擁有多于一個控制器的選項,以適應多個存儲器總線接口的要求。另外一些選項可提供對時鐘控制方法、CAS 延遲、突發長度和引腳分配的控制。

評論