基于ARM和FPGA的時間同步儀控制單元設計

2.4 以太網接口電路設計

網絡傳輸模塊使用Devicom公司研發的一款快速以太網控制芯片DM9000A,其內部集成了10/100 MB物理層接口,支持8/16位數據總線,內置16 kB的SRAM,用于收發緩沖。

S3C2440A內部沒有集成專用的以太網控制器,所以需要外掛一個以太網控制器。系統采用DM9000A作為以太網的物理層接口。S3C2440A與DM9000A的連接如圖所示。S3C2440A的數據總線LDATA15~LDATA0與DM9000A的SD15~SD0連接;地址線LADDR3與DM9000A的CMD連接;片選DM_CS與DM9000A的CS連接;DM_IOR/DM_IOW分別與DM9000A的IOR/IOW連接;EINT8與DM9000A的INT連接。以太網控制器DM9000A的工作地址為0X30 0,因為S3C2440A的地址線LADDR3與DM9000A的CMD連接,所以對其進行操作時分為以0X300作為地址端口和0X304作為數據端口。

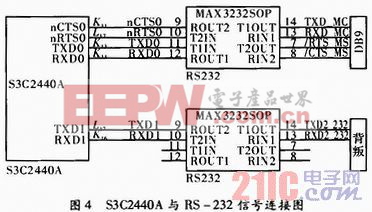

2.5 RS232接口電路設計

S3C2440A集成了3個串口UART0、1、2,文中用到UART0,UART1,其中UART0作為標準串口通信,與宿主機相連用于系統調試、超級終端控制和文件收發;UART1與單片機ATMEGA128連接,其作用是傳遞導航電文和狀態參數給GSG單板。圖4為S3C2440A與RS-232信號連接圖,其中上方的MAX3232SOP作為UART0使用,下方的MAX3232SOP作為UART1使用。本文引用地址:http://www.104case.com/article/148830.htm

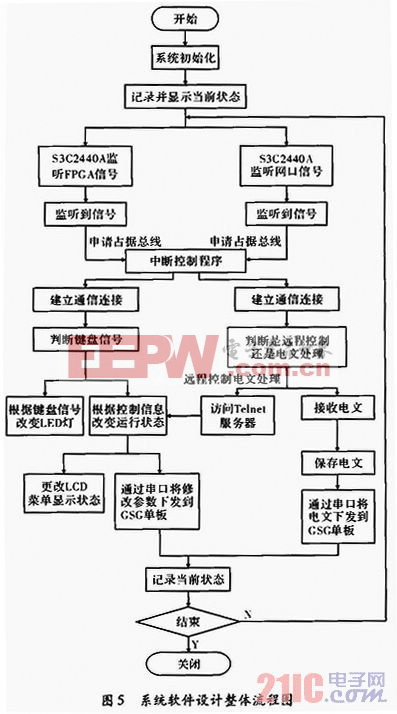

3 系統軟件設計

系統的軟件部分是在Linux操作系統下實現的。結合控制系統的功能分為人機交互、參數設定、電文處理、遠程控制4個模塊,圖5為軟件設計流程圖。

評論