FPGA時(shí)序收斂分析

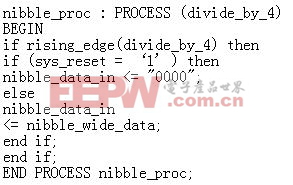

某些設(shè)計(jì)采用單個(gè)主時(shí)鐘的分割版本來處理反序列化數(shù)據(jù)。以下 VHDL 代碼(nibble_proc進(jìn)程)舉例說明了按系統(tǒng)時(shí)鐘頻率的四分之一采集的數(shù)據(jù)。

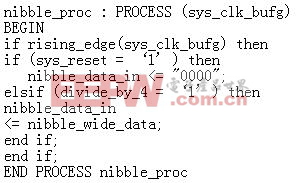

看起來好像一切都已經(jīng)同步化,但是 nibble_proc 采用乘積項(xiàng) divide_by_4 對來自時(shí)鐘域sys_clk_bufg 的 nibble_wide_data 進(jìn)行采樣。由于路由延遲,divde_by_4 與 sys_clk_bufg 之間并無明確的相位關(guān)系。將 divide_by_4 轉(zhuǎn)移到 BUFG 也于事無補(bǔ),因?yàn)榇诉M(jìn)程會(huì)產(chǎn)生路由延遲。解決方法是將 nibble_proc 保持在 sys_clk_bufg 域,并且采用 divide_by_4 作為限定符,如下所示。

時(shí)序約束的重要性

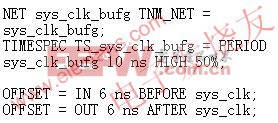

如果您希望自己的邏輯正確運(yùn)行,則必須采用正確的時(shí)序約束。如果您已經(jīng)慎重確保代碼全部同步且注冊了全部 I/O,則這些步驟可以顯著簡化時(shí)序收斂。在采用上述代碼并且假定系統(tǒng)時(shí)鐘為100MHz 時(shí),則只需四行代碼就可以輕松完成時(shí)序約束文件,如下所示:

請注意:賽靈思 FPGA 中 I/O 注冊邏輯的建立與保持時(shí)間具有很高的固定性,在一個(gè)封裝中切勿有太大更改。但是,我們?nèi)匀徊捎盟鼈儯饕米骺纱_保設(shè)計(jì)符合其系統(tǒng)參數(shù)的驗(yàn)證步驟。

三步簡單操作

僅需遵循以下三步簡單操作,設(shè)計(jì)人員即可輕松實(shí)施可靠的代碼。

• 切勿讓綜合工具猜測您的預(yù)期。采用賽靈思原語對所有 I/O 引腳和關(guān)鍵邏輯進(jìn)行明確定義。確保定義 I/O 引腳的電氣特性;

• 確保邏輯 100% 同步,并且讓所有邏輯參考主時(shí)鐘域;

• 應(yīng)用時(shí)序約束確保時(shí)序收斂。

只要遵循上述三個(gè)步驟,您就能夠消除綜合與時(shí)序?qū)е碌牟町悺叱@兩個(gè)主要障礙會(huì)讓您獲得具有 100% 可靠性的代碼。

評論