FPGA時序收斂分析

異步邏輯的劣勢本文引用地址:http://www.104case.com/article/148674.htm

異步代碼會產生難以約束、仿真及調試的邏輯。異步邏輯往往產生間歇性錯誤,而且這些錯誤幾乎無法重現(xiàn)。另外,無法生成用于檢測異步邏輯所導致的錯誤的測試平臺。

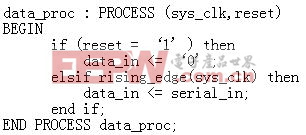

雖然異步邏輯看起來可能容易檢測,但是,事實上它經(jīng)常不經(jīng)檢測;因此,設計人員必須小心異步邏輯在設計中隱藏的許多方面。所有鐘控邏輯都需要一個最短建立與保持時間,而且這一點同樣適用于觸發(fā)器的復位輸入。以下代碼采用異步復位。在此無法為了滿足觸發(fā)器的建立與保持時間需求而應用時序約束。

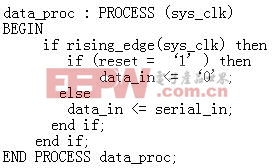

下列代碼采用同步復位。但是,大多數(shù)系統(tǒng)的復位信號都可能是按鍵開關,或是與系統(tǒng)時鐘無關的其它信號源。盡管復位信號大部分情況是靜態(tài)的,而且長期處于斷言或解除斷言狀態(tài),不過其水平仍然會有所變化。相當于系統(tǒng)時鐘上升沿,復位解除斷言可以違反觸發(fā)器的建立時間要求,而對此無法約束。

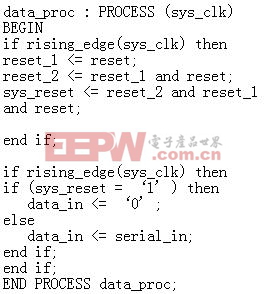

只要我們明白無法直接將異步信號饋送到我們的同步邏輯中,就很容易解決這個問題。以下代碼創(chuàng)建一個稱為 sys_reset 的新復位信號,其已經(jīng)與我們的系統(tǒng)時鐘 sys_clk 同步化。在異步邏輯采樣時會產生亞穩(wěn)定性問題。我們可以采用與階梯的前幾級進行了’與’運算的梯形采樣降低此問題的發(fā)生幾率。

至此,假定您已經(jīng)慎重實現(xiàn)了所有邏輯的同步化。不過,如果您不小心,則您的邏輯很容易與系統(tǒng)時鐘脫節(jié)。切勿讓您的工具鏈使用系統(tǒng)時鐘所用的本地布線資源。那樣做的話您就無法約束自己的邏輯。切記要明確定義所有的重要邏輯。

以下 VHDL 代碼采用賽靈思 BUFG 原語強制 sys_clk 進入驅動低延遲網(wǎng)絡 (low-skew net) 的專用高扇出緩沖器。

評論