使用FPGA解決DSP設(shè)計(jì)難題

本文引用地址:http://www.104case.com/article/148230.htm

本文引用地址:http://www.104case.com/article/148230.htm

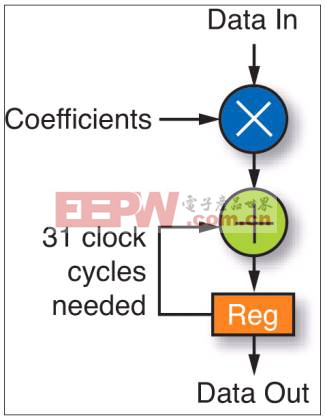

圖3:傳統(tǒng)DSP中的MAC實(shí)現(xiàn)方案

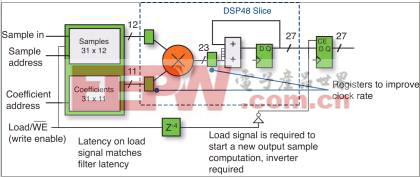

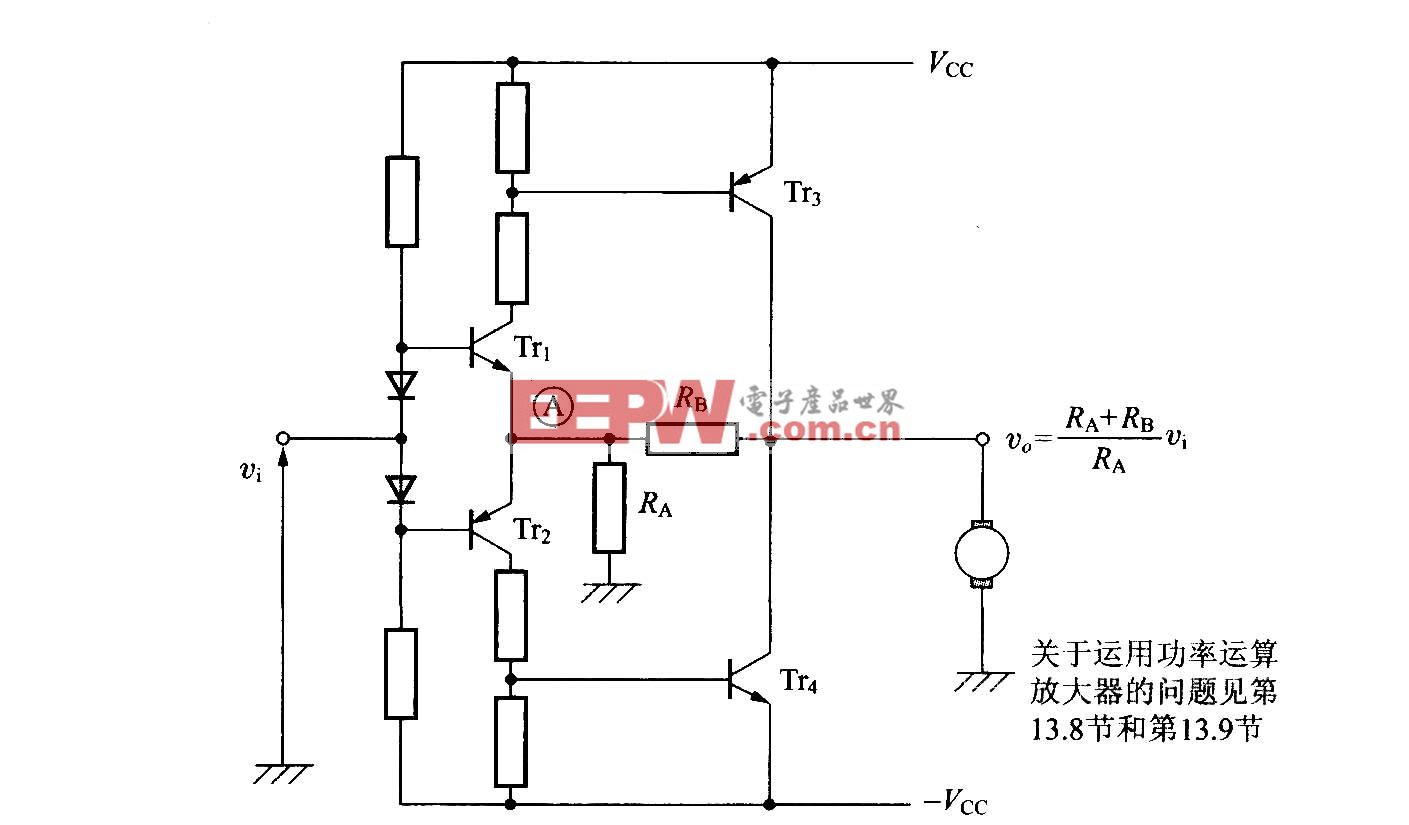

而FPGA提供了許多不同的實(shí)現(xiàn)和優(yōu)化選擇。如果需要高資源效率的實(shí)現(xiàn),MAC引擎法則相當(dāng)不錯(cuò)。還是以31抽頭濾波器為例來(lái)說(shuō)明濾波器規(guī)范對(duì)所需邏輯資源的影響,這種實(shí)現(xiàn)方案的框圖如圖4所示。

圖4:FPGA中的MAC引擎FIR濾波器

這種設(shè)計(jì)需要存儲(chǔ)器存儲(chǔ)數(shù)據(jù)和系數(shù),可以混合采用FPGA內(nèi)部的RAM和ROM。RAM用于存儲(chǔ)數(shù)據(jù)樣本,故而采用循環(huán)的RAM緩沖器實(shí)現(xiàn)。字的數(shù)量與濾波器抽頭數(shù)相等,位寬按樣本大小設(shè)置。ROM用于存儲(chǔ)系數(shù)。在最差情況下,字的數(shù)量與濾波器抽頭的數(shù)量相等,但如果存在對(duì)稱(chēng),則可以減少字的數(shù)量。位寬必須足以支持最大的系數(shù)。因?yàn)閿?shù)據(jù)樣本和系數(shù)數(shù)據(jù)都隨每個(gè)周期改變,所以需要全乘法器。累加器負(fù)責(zé)將產(chǎn)生的結(jié)果累加起來(lái)。因?yàn)殡S著濾波器采集數(shù)據(jù),累加器的輸出會(huì)隨每個(gè)時(shí)鐘周期改變,所以需要捕捉寄存器。當(dāng)全套N個(gè)樣本完成累加后,輸出寄存器負(fù)責(zé)捕捉最終結(jié)果。

如果采用MAC模式,DSP48則非常適合,因?yàn)?a class="contentlabel" href="http://www.104case.com/news/listbylabel/label/DSP">DSP48Slice內(nèi)含輸入寄存器、輸出寄存器和加法器單元。實(shí)現(xiàn)31抽頭MAC引擎需要的資源包括一個(gè)DSP48、一個(gè)18kb塊RAM和9個(gè)邏輯片。另外,還需要一些邏輯片用于采樣、系數(shù)地址生成和控制。如果FPGA內(nèi)置有600MHz的時(shí)鐘,則在一個(gè)-3速度等級(jí)的Xilinx7系列器件中,該濾波器能夠以19.35MHz或1,935MSps的輸入采樣速率運(yùn)行。

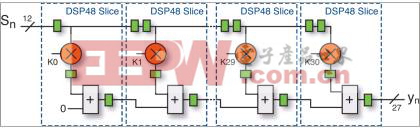

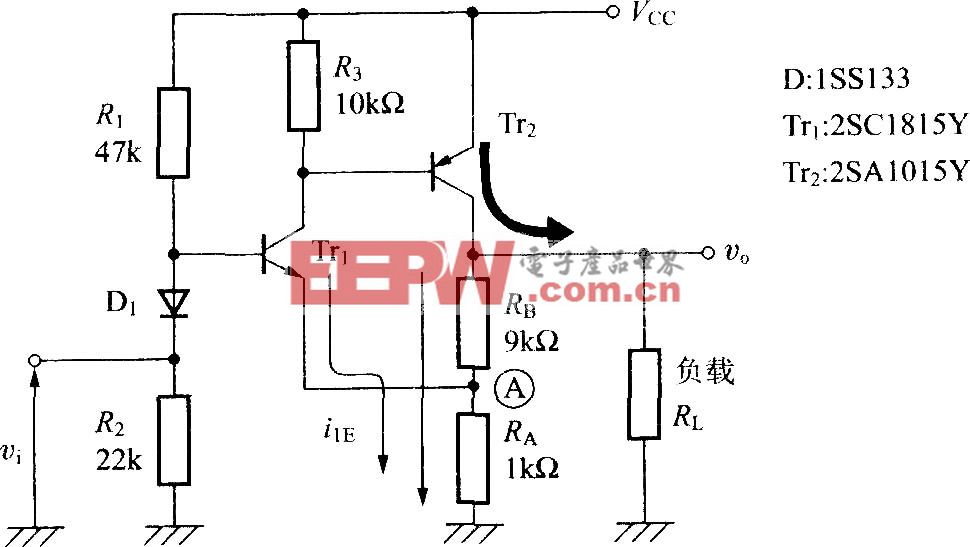

如果系統(tǒng)規(guī)范需要更高性能的FIR濾波器,則可采用并行結(jié)構(gòu)來(lái)實(shí)現(xiàn)。圖5顯示了直接I型實(shí)現(xiàn)方案的框圖。

圖5:FPGA中的直接I型濾波器

直接I型濾波器結(jié)構(gòu)能夠在FPGA中實(shí)現(xiàn)最高性能。這種結(jié)構(gòu)(通常也被稱(chēng)作脈動(dòng)FIR濾波器)采用流水線和加法器鏈,使DSP48 Slice發(fā)揮出最高性能。輸入饋送到用作數(shù)據(jù)樣本緩沖器的級(jí)聯(lián)寄存器;每個(gè)寄存器向DSP48提供一個(gè)樣本,然后乘以對(duì)應(yīng)的系數(shù);加法器鏈存儲(chǔ)部分乘積,然后依次相加,從而得到最終結(jié)果。

這種設(shè)計(jì)無(wú)需外部邏輯電路支持濾波器,并且該結(jié)構(gòu)可擴(kuò)展用于支持任意數(shù)量的系數(shù)。因?yàn)闆](méi)有高扇出的輸入信號(hào),所以這種結(jié)構(gòu)能夠?qū)崿F(xiàn)最高性能。實(shí)現(xiàn)31抽頭FIR濾波器僅需要31個(gè)DSP48邏輯片。如果FPGA內(nèi)置有600MHz的時(shí)鐘,則在一個(gè)-3速度等級(jí)的Xilinx7系列器件中,該濾波器能夠以600MHz或600MSps的輸入采樣速率運(yùn)行。

從這個(gè)實(shí)例可以清晰地看出,F(xiàn)PGA不僅在性能上顯著超越了傳統(tǒng)的數(shù)字信號(hào)處理器,而且要求的時(shí)鐘速率也顯著降低(因此,功耗也顯著降低)。

這個(gè)實(shí)例只反映了采用PFGA實(shí)現(xiàn)FIR濾波器的兩種技術(shù)。為了充分利用數(shù)據(jù)采樣率規(guī)范,可對(duì)該器件進(jìn)行進(jìn)一步定制,此時(shí),數(shù)據(jù)采樣率可在連續(xù)MAC運(yùn)算極值和全并行運(yùn)算極值之間。您還可考慮在包括對(duì)稱(chēng)系數(shù)、插值、抽取、多通道或多速率的資源利用與性能之間進(jìn)行更多的權(quán)衡取舍。Xilinx CORE Generator?或System Generator(系統(tǒng)發(fā)生器)實(shí)用工具可以幫助用戶(hù)充分利用這些設(shè)計(jì)變量和技術(shù)。

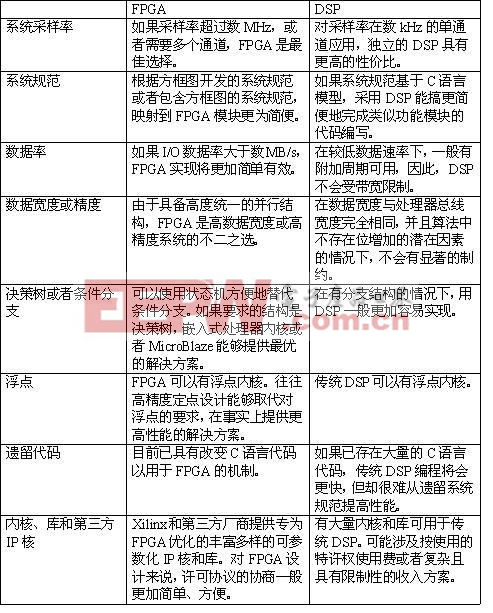

在傳統(tǒng)DSP和FPGA之間選擇

傳統(tǒng)的數(shù)字處理器已經(jīng)有多年的應(yīng)用歷史,當(dāng)然有為特定問(wèn)題提供最佳解決方案的實(shí)例。如果系統(tǒng)采樣率低于數(shù)kHz且為單通道方案,DSP可能是不二之選。但是,當(dāng)采樣率增加到數(shù)MHz以上,或者如果系統(tǒng)要求多通道,F(xiàn)PGA就越來(lái)越有優(yōu)勢(shì)。在高數(shù)據(jù)率條件下,DSP可能只能勉為其難地在不造成任何損耗的情況下采集、處理和輸出數(shù)據(jù)。這是因?yàn)樵谔幚砥髦写嬖诖罅康墓蚕碣Y源、總線乃至內(nèi)核。然而,F(xiàn)PGA卻能夠?yàn)槊宽?xiàng)功能提供專(zhuān)門(mén)的資源。

DSP是基于指令而非基于時(shí)鐘的器件。一般來(lái)講,對(duì)單個(gè)樣本上的任何數(shù)學(xué)運(yùn)算需要三到四條指令。數(shù)據(jù)必須首先經(jīng)輸入端采集,再發(fā)送到處理內(nèi)核,每完成一次運(yùn)算后再循環(huán)通過(guò)內(nèi)核,然后發(fā)送到輸出端。相比之下,F(xiàn)PGA基于時(shí)鐘,所以每個(gè)時(shí)鐘周期都有可能在輸入數(shù)據(jù)流上進(jìn)行一次數(shù)學(xué)運(yùn)算。

由于DSP的運(yùn)算以指令或代碼為基礎(chǔ),編程機(jī)制為標(biāo)準(zhǔn)C語(yǔ)言,或者在需要更高性能的情況下,采用低級(jí)匯編語(yǔ)言。這種代碼可能包含高級(jí)的決策樹(shù)或者轉(zhuǎn)移操作,而難以在FPGA中實(shí)現(xiàn)。例如,存在大量的用于執(zhí)行如音頻和電話編解碼器之類(lèi)的預(yù)定義功能或標(biāo)準(zhǔn)的遺留代碼。

FPGA廠商和第三方合作伙伴已經(jīng)意識(shí)到將FPGA用于高性能DSP系統(tǒng)的優(yōu)勢(shì),并且如今已有許多IP核廣泛應(yīng)用于視頻、圖像處理、通信、汽車(chē)、醫(yī)療和軍用等大部分垂直應(yīng)用市場(chǎng)。與將高級(jí)系統(tǒng)框圖映射成為C語(yǔ)言代碼的DSP設(shè)計(jì)相比,將高級(jí)系統(tǒng)框圖分解為FPGA模塊和IP核會(huì)更加簡(jiǎn)便易行。

從DSP轉(zhuǎn)向FPGA

研究一些主要標(biāo)準(zhǔn)將有利于在傳統(tǒng)DSP和FPGA之間作出選擇(請(qǐng)參見(jiàn)表1)。

表1: 傳統(tǒng)DSP和FPGA之間的比較

軟件編程人員的數(shù)量遠(yuǎn)遠(yuǎn)超過(guò)硬件設(shè)計(jì)人員的數(shù)量,這已是不爭(zhēng)的事實(shí)。DSP編程人員的數(shù)量與FPGA設(shè)計(jì)人員的數(shù)量之間的關(guān)系也是如此。不過(guò),讓系統(tǒng)架構(gòu)師或者DSP設(shè)計(jì)人員轉(zhuǎn)為使用FPGA的難度,并不像讓軟件編程人員轉(zhuǎn)為從事硬件設(shè)計(jì)那么大。有大量的資源可以大大簡(jiǎn)化DSP算法開(kāi)發(fā)和FPGA設(shè)計(jì)工作的學(xué)習(xí)過(guò)程。

主要的障礙是從基于樣本和事件的方法轉(zhuǎn)向基于時(shí)鐘的問(wèn)題描述和解決方案。如果能夠在設(shè)計(jì)流程的系統(tǒng)架構(gòu)和定義階段就能夠完成,對(duì)這種轉(zhuǎn)換的理解和應(yīng)用就會(huì)簡(jiǎn)單得多。由不同的工程師和數(shù)學(xué)專(zhuān)家來(lái)定義系統(tǒng)架構(gòu)(DSP算法和FPGA設(shè)計(jì)在某種程度上相互孤立)是很尋常的事情。當(dāng)然,如果每個(gè)成員對(duì)其他小組成員面臨的難題有一定程度認(rèn)識(shí)的話,這個(gè)過(guò)程會(huì)順利得多。要掌握FPGA方案,架構(gòu)師不需要精通FPGA設(shè)計(jì)。只需對(duì)器件、資源和工具有基本的了解就夠了。

評(píng)論