使用FPGA解決DSP設計難題

由于DSP能夠迅速測量、過濾或壓縮實時模擬信號,因此DSP在電子系統設計中非常重要。這樣,DSP有助于實現數字世界與真實(模擬)世界的通信。但是隨著電子系統變得越來越精細,需要處理多個模擬信號源,工程師們不得不作出艱難的決策。是使用多個DSP并使其功能與系統的其余部分同步,還是使用一個能夠實現多個功能的帶精細軟件的高性能DSP更具優勢?

由于現在的系統很復雜,在許多情況下,單DSP的實現方案的往往沒有足夠的處理能力。同時,系統架構也不能滿足多芯片系統的成本、復雜性和功耗要求。

FPGA現已成為需要高性能DSP功能的系統的絕佳選擇。事實上,與獨立的數字信號處理器相比,FPGA技術一般可以為DSP難題提供更加簡單的解決方案。要了解其中的原因,需要回顧一下DSP的起源和發展過程。

專用微處理器

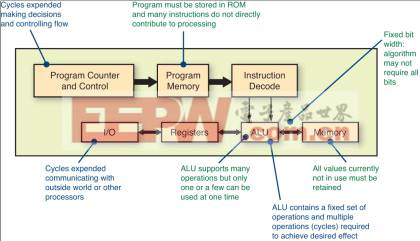

在過去的二十多年里,傳統的DSP架構一直在竭力跟上日益增長的性能要求的步伐。隨著視頻系統大踏步地邁進高清和3D時代,并且通信系統為實現更高帶寬已經將現有技術發揮到極致,設計師們需要可替代的實現策略。用于實現數字信號處理算法的硬件不外乎以下三種基本器件之一:微處理器、邏輯電路和存儲器。有些設計可能還需要額外硬件來實現模數轉換(A/D)、數模轉換(D/A)以及高速數字接口。

傳統的數字信號處理器是設計用于實現專門目的的微處理器。這類處理器非常適合用于處理算法密集型任務,但是性能卻受到時鐘速率及其內部設計順序性的限制。這限制了它們對輸入數據采樣每秒最多執行的運算次數。一般來講,每執行一次算術邏輯單元(ALU)運算需要三或四個時鐘周期。多核架構可以提高性能,但是提升幅度有限。因此,采用傳統信號處理器的設計必須重復利用架構單元來實現算法。對于每次執行的加、減、乘或其他任何基本運算,不論是內部還是外部反饋,每次執行都必須循環通過ALU。

遺憾的是,在處理當今眾多的高性能應用時,典型的DSP難以滿足系統要求。過去已經提出過多種解決方案,包括在一個器件中使用多個ALU或者在一塊板上使用多個DSP器件;不過這類方案往往會大大增加成本,并且只會將問題轉移到另外一個領域。比如,用多個器件提高性能遵循指數曲線。要使性能提高一倍,需要用兩個器件,若要再提高一倍,則需要用四個器件,依此類推。此外,程序員關注的重點往往會從信號處理功能轉移到多個處理器和內核之間的任務調度上。這會產生大量的附加代碼,而且這些代碼會成為系統開銷,而不是用于解決眼前的數字信號處理問題。

FPGA 技術的引進為解決DSP方案與日俱增的復雜性帶來了福音。FPGA最初開發的目的是為了整合和集中分立的存儲器和邏輯電路,以實現更高的集成度、更出色的性能和更高的靈活性。FPGA技術現已成為目前使用的幾乎所有高性能系統的一個重要組成部分。相比傳統DSP,FPGA是由可配置邏輯陣列(CLB)、存儲器、DSP邏輯片(Slice)和一些其他元件組成的統一陣列構成的巨大并行結構。它們可以使用VHDL和Verilog等高級描述語言進行編程,或者在框圖中使用系統生成器進行編程。FPGA還提供許多專用功能和IP核,用來以高度優化的方式直接完成實現方案。

FPGA內的數字信號處理器的主要優勢是能夠定制滿足系統要求的方案。這意味著在多通道或高速系統中,用戶可以充分利用器件內部的并行性,從而最大限度地提高性能,而對于低速系統,則可以更多地采用串行方式完成設計。因此,設計人員可以定制滿足算法和系統要求的方案,而不是取期望的理想設計的折衷方案來迎合純順序器件的諸多局限。另外,超高速I/O通過最大限度地提高從捕捉經處理鏈再到最終輸出的數據流,可進一步降低成本并減少瓶頸問題。

下面以一個同時使用傳統DSP架構和FPGA架構的FIR濾波器實現方案為例,來說明每種解決方案的優劣。

數字FIR濾波器實例

有限脈沖響應(FIR)濾波器是一種使用最廣的數字信號處理元件。設計人員使用濾波器來改變數字信號的幅度或頻譜,通常用于隔離或突出樣本數據頻譜中的特定區域。從這個角度來講,可以把濾波器視為信號的預處理方式。在典型的濾波器應用中,輸入數據樣本通過小心同步的數學運算與濾波器系數相結合(這取決于濾波器的類型和實現策略),隨后數據樣本進入下一個處理階段。如果數據源和目的地都是模擬信號,則數據樣本必須首先通過A/D轉換器,而結果則必須饋送給D/A轉換器。

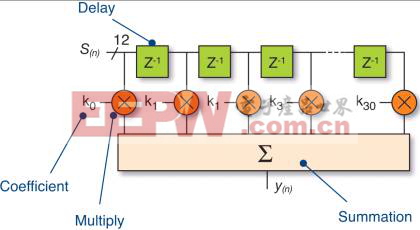

最簡單的FIR濾波器是通過用一系列的延遲元件、乘法器和加法器樹或加法器鏈來實現的。

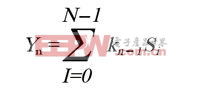

下面的等式是單通道FIR濾波器的數學表達式:

公式1

該等式中的各項分別表示輸入樣本、輸出樣本和系數。假設S為連續的輸入樣本流,Y為經濾波后產生的輸出樣本流,那么n和k則對應特定的瞬時時間。這樣,若要計算時間n時的輸出樣本Y(n),則需要一組在N個不同時間點的樣本,即:S(n)、S(n-1)、s(n-2)、…s(n-N+1)。將這組N個輸入樣本乘以N個系數并求和,便可得出最終結果Y。

圖2是一個簡單的31抽頭FIR濾波器(長度N=31)的框圖。

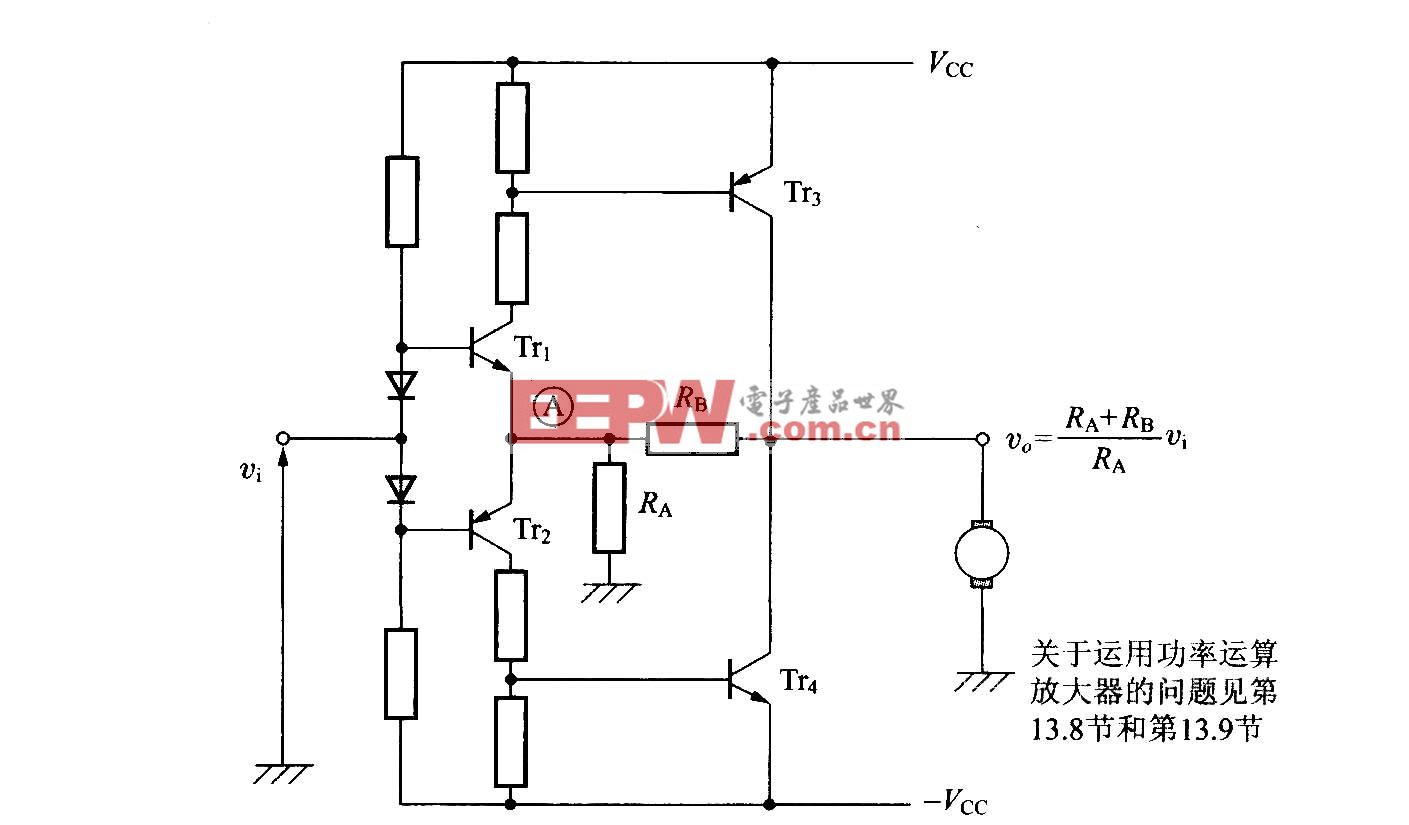

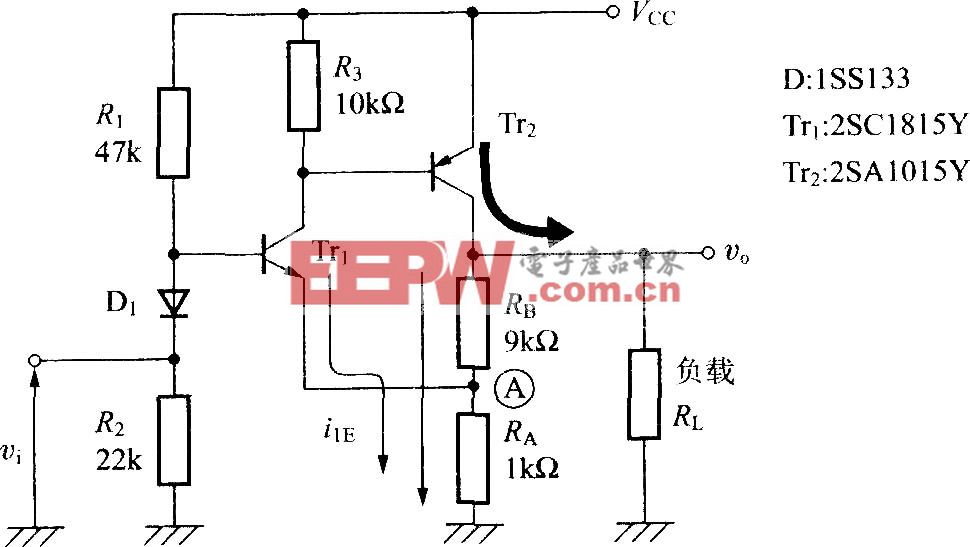

圖1:傳統的DSP架構

圖2:長度為31抽頭的FIR濾波器

在選擇濾波器的理想長度和系數值時,有多種設計工具可供使用。其目的是通過選擇適當的參數來實現所需的濾波器性能。參數選擇最常用的設計工具是MATLAB。一旦選定了濾波器參數,就可以用數學等式實現。

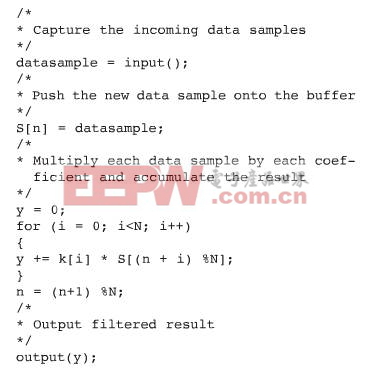

實現FIR濾波器的基本步驟包括:

1. 對輸入數據流采樣;

2. 在緩沖區組織輸入樣本,以便讓每個捕捉到的樣本與每項濾波器系數相乘;

3. 讓每個數據樣本與每項系數相乘,并累加結果;

4. 輸出濾波結果。

使用“相乘累加法”在處理器上實現FIR濾波器的典型C語言程序,如下列代碼所示。

圖3所示的實現方案被稱為相乘累加或MAC型實現方案。這基本上就是用傳統的DSP處理器實現濾波器的方法。采用內核時鐘速率為1.2GHz的典型DSP處理器并以這種方式實現的31抽頭FIR濾波器的最高性能約為9.68MHz,或最大的輸入數據率為968MS/s。

評論