一種基于ARM和FPGA的環形緩沖區接口設計

2.3 接收程序設計

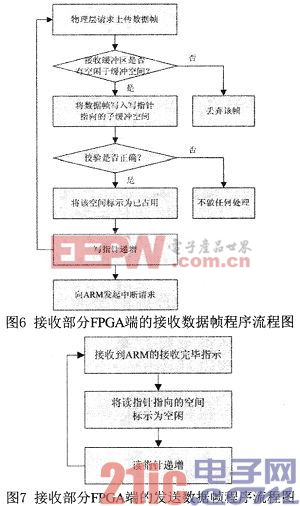

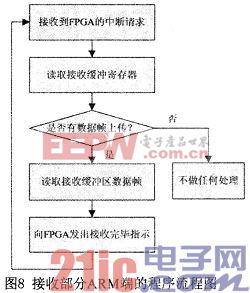

數據的接收同樣包括ARM端和FPGA端兩部份程序,相互配合共同完成ARM從FPGA讀取數據幀的流程。FPGA端的程序主要有兩個任務,一是負責把從物理層接收到的數據幀寫入接收緩沖區中,并向ARM發出中斷請求接收數據幀,另一個是在得到ARM接收完畢確認后處理好接收緩沖區的空間釋放;ARM端的程序負責從FPGA接收緩沖區中讀取數據幀。

接收部分FPGA端仍然是利用子緩沖空間的忙閑狀態與讀寫指針的變化來控制數據幀的寫入和讀取,并實現接收完來自物理層數據幀后向ARM發出發起中斷,當ARM讀取數據幀后釋放子緩沖區空間,程序結構如圖6和圖7所示。本文引用地址:http://www.104case.com/article/148003.htm

接收部分ARM端的程序流程如圖8所示,當ARM接收到FPGA的中斷后,判斷是否有數據幀要上傳,若不是則不做任何處理;若是則從統一編址的接收緩沖區讀取數據幀,然后向FPGA發出接收完畢指示以便于FPGA及時釋放相應的子緩沖空間。

3 測試結果

本方案在實驗室自行開發設計的BCNG2440寬帶無線收發平臺上進行了測試運行。該平臺主要由Samsung公司S3C2240型的ARM CPU和Xi-linx公司的V5系列SX95T型FPGA組成。物理層最高速率為1Mb/s,通過變化來自應用層的數據包大小和的間隔來改變用戶速率,用以測試

ARM和FPGA的數據緩沖區和匹配功能。實際測試和運行表明,此方案是有效而合理的。

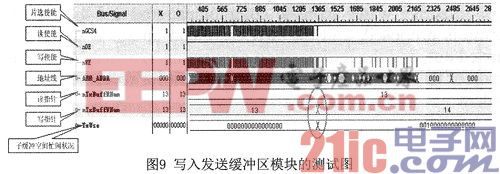

以發送緩沖區設計為例,圖9給出了用chipscope觀察該部分設計方法的正確性。ARM發送數據幀到發送緩沖區后FPGA的內部變化如圖7所示。可以看到ARM發送的數據幀寫入了FPGA中序號為13的子緩沖空間,結束時寫指針(nTxBuffWNum)遞增指向了序號為14的子緩沖空間,同時序號為13(實際上是第14個,這是由于序號是從0到15)的子緩沖空間被標示為占用。從圖中也可以看到前面寫入的數據幀已經發送,其它子緩沖空間都為空閑狀態,讀指針(nTxBuffRNum)也是正常變化的。

應該指出的是,本方案具備良好的擴展性。通過改變子緩沖區的數目和子緩沖區的大小,可以用來對不同的應用情況進行速率匹配。

4 結語

本文介紹了基于ARM和FPGA的環形緩沖區的設計方法,實現簡單并便于擴展。測試結果表明此方法能實現ARM和FPGA之間數據的有效傳輸。對網絡協議的實現具有重要的參考價值。

fpga相關文章:fpga是什么

評論