采用低成本FPGA構建IP監視攝像系統

IP監視攝像機參考設計

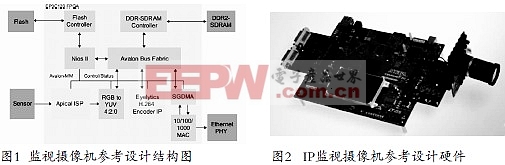

本文引用地址:http://www.104case.com/article/142476.htm圖1所示為IP監視攝像機參考設計的頂層結構圖和硬件,它主要面向新一代HD(>1MP)WDR傳感器。IP監視攝像機參考設計結合了Altera以及多家合作伙伴的硬件和軟件知識產權。

圖2顯示了參考設計的硬件平臺,基于Cyclone III EP3C120開發板。Aptina WDR傳感器像素數據被送入Apical的圖像傳感器流水線(ISP)。輸出數據是YUV 4:2:0格式,寫入到外部DDR2 SDRAM的幀緩沖中,它使用了Altera視頻和圖像處理(VIP)套裝提供的組件。然后,使用EyeLytics提供的內核,以H.264格式對視頻數據進行編碼,支持(在這一應用中)3級基線/主要類視頻流,通過以太網在遠程主機上觀看。散射收集直接存儲器訪問(SGDMA)控制器支持Altera三速以太網(TSE)MegaCore功能,將編碼后的視頻流通過以太網傳送到遠程客戶端。

寬動態范圍傳感器

Aptina MT9M033是0.33" 720p60 WDR CMOS傳感器,主要用于監視攝像機市場。傳感器和鏡頭組合安裝在“頂板”上,通過I/O轉換板將其連接至Cyclone III EP3C120開發板。

圖像傳感器流水線

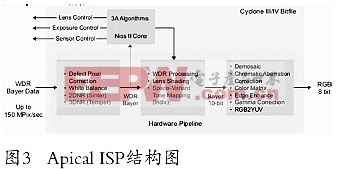

CMOS WDR傳感器沒有片內圖像流水線處理功能,以RAW/Bayer格式輸出圖像數據,每像素為20比特。可以采用下式來計算傳感器輸出的大量原始數據:20比特/像素x(1280x720)像素/幀x60幀/s=>1Gbit/s。由于數據量過大,因此很難將新一代WDR傳感器連接至監視解決方案中經常使用的ASSP。因此,FPGA是高效處理數據的理想選擇。Apical的ISP(圖3)包括以下功能:

● 去除熱點像素,抑制噪聲(提供空間和時域IP內核)。

● 使用Apical獲獎的專利Iridix IP內核實現單位像素高級色調映射功能

● 高級去馬賽克和顏色校正

fpga相關文章:fpga是什么

評論