從頭到尾構建混合信號高集成度系統(SOC)的步驟(5):電路仿真

Dave:大概如此。我知道我們需要一個輸出放大器,所以我們獲得了這方面的一些幫助。輸出放大器的規格易于制定,但在CMOS中是一個需要技巧來構建的模塊。在此之后,我們開始依次增加均衡器級,在每次添加后利用電纜模型進行仿真。我們使均衡功能有效,但還要記錄失真、功率預算和DIE面積預算。

本文引用地址:http://www.104case.com/article/141904.htmTamara博士:看似有許多要考慮的事情。

Dave:是,但魔鬼就在細節里。一位老員工有次對我說,(對此種開發來說)“偏執狂才是正確的心理狀態。”

Tamara博士:伍迪艾倫有次說,“偏執狂知道所有事實。”

Dave:說得太對了!

Tamara博士:好了,現在我們有了所有模擬處理級,接下來如何測試整個系統呢?

Dave:在學校里,你只是運行功能仿真測試。而在業內,我們是設計具有制造可行性的電路。制造工藝具有容差。摻雜程序具有范圍,晶體管因之能夠運行得稍快或稍慢一些。我們需要仿真最佳和最差條件,來獲得我們器件的最佳產率。

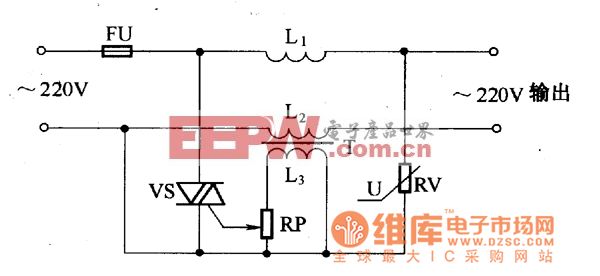

Tamara博士:我想你還需要考慮溫度。這些組合的圖表看上去可能像這個:

Dave:良好的開端!現在你需要解釋無源元件——如電阻和電容——的容差。你能看到情形的數量會如何激增而使你永遠不能完成設計!

Tamara博士:你還需要做一些事情來減少你需要運行的仿真的數量。或者至少限制參數值對制造容差的依賴性。

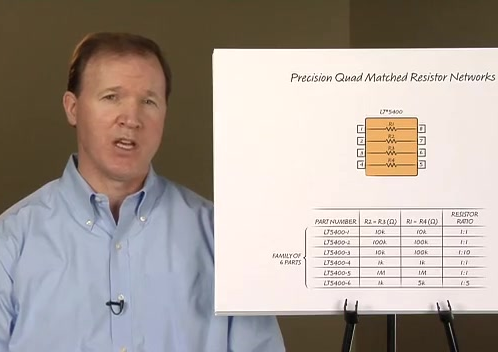

Dave:就這樣了。有許多設計技巧可供使用。一種是使用電阻器的比率值而非精確值。兩個電阻器值可以一起增大或減小,所以比率在某種程度是不變的。盡管在所有情況中我們都會使用少量動態余量(過度設計)來確保我們能夠滿足我們的目標要求。

Tamara博士:你的過度設計量達到多少?10%?

Dave:我希望我們進行10%的過度設計。不過通常我們沒有這樣大的余地。我們的2毫米×2毫米原始尺寸目標和功耗技術規格將會限制我們的實現能力。

Tamara博士:你還從未談到靜電放電(ESD)。我知道這可能是一個挑戰。

Dave:實際上我們有ESD方面的專家來幫助我們將合適的電路用在正確的引腳上。這里也有重要的權衡考慮。ESD二極管具有很大的容性且隨電壓而變化,所以在我們應用ESD時我需要重新運行失真仿真。

Tamara博士:測試呢?你在設計中如何幫助進行器件測試?

Dave:對于數字器件,我們有一種稱為‘掃描’的測試,它包括一些特別的測試,例如把所有的觸發器串聯起來。運行掃描測試可保證所有電路鏈中的所有觸發器的有效性。還有一個叫做“覆蓋率”的參數,它讓我們知道我們實際上測試了數字器件的多大部分。該參數最好能達到90%以上。

Tamara博士:模擬測試呢?

Dave:在設計過程中,我們制定了一個測試計劃,該計劃描述了將在生產中如何對每個模塊進行測試。通常,該測試會揭示缺陷且常常導致進入特別測試模式。

Tamara博士:哪種測試模式?

Dave:嗯,這里有一個易于理解的例子:我們需要知道我們的內置振蕩器的運行頻率,所以我們設計一個簡單的基于外部標準的時序脈沖的頻率計數器。基本上,然后我們用一個寄存器來支持該功能,并從另一個寄存器讀回結果。這種模式非常快而干凈,并可節省測試時間。

Tamara博士:還有其他模式嗎?

Dave:有些東西是不能說的,有權利保護。(他說的時候眨了個眼)我餓了。

Tamara博士:很好。來杯啤酒和一大塊那種鮭魚怎么樣?

Dave:好,聽你的!

評論