滿足28 nm迫切的低功耗需求

其他在28-nm節(jié)點尋求絕對最低功耗的主要半導體供應商也選擇了28LP工藝,正如Qualcomm所宣稱的那樣:“Qualcomm與TSMC合作,推出了我們的Snapdragon™ S4類處理器,包括Snapdragon S4 MSM8960™,它是高度集成的雙核SoC,設計滿足了前沿智能電話和平板電腦的低功耗需求。Snapdragon S4類處理器采用了TSMC非常復雜的28LP工藝,使Qualcomm能夠突破性的實現(xiàn)了高性能和超低功耗的移動設備。”TSMC新聞發(fā)布,“TSMC 28nm技術達到量產(chǎn)”,2011年10月24號:

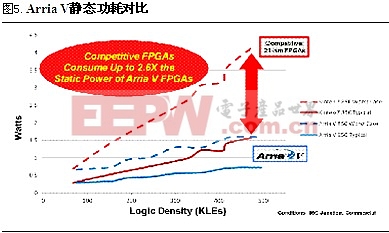

本文引用地址:http://www.104case.com/article/136059.htm在低功耗基礎上,Altera還采取了其他措施來降低28LP器件的靜態(tài)功耗,包括大量使用“低泄漏”晶體管等,從而降低了靜態(tài)電流。此外,Cyclone V和Arria V系列還提供一些可以禁用的器件特性,包括收發(fā)器、I/O塊、PCI Express®模塊、存儲器模塊以及分段式PLL等。這些特性相結合,與前一代FPGA相比,器件靜態(tài)功耗降低了70%。例如,Arria V系列的器件功耗在500K LE時不到750mW,比目前的中端和高端40-nm FPGA靜態(tài)功耗低得多。而競爭28-nm FPGA的靜態(tài)功耗是Arria V FPGA的2.6倍。 Arria V靜態(tài)功耗對比顯示了Arria V GX器件的典型靜態(tài)功耗,以藍色實線表示,而以藍色點線表示最差情況下的功耗。類似的,紅色實線表示競爭中端28-nm FPGA的典型靜態(tài)功耗,點線表示最差情況下的功耗。借助這些特性,在同類FPGA中,Arria V器件的靜態(tài)功耗是最低的。

低動態(tài)功耗體系結構

除了低靜態(tài)功耗,Altera Cyclone V和Arria V器件的動態(tài)功耗也較低,從而實現(xiàn)了最低總功耗。Altera從28LP工藝開始采用了降低動態(tài)功耗的方法,主要面向低功耗應用,包括,便攜式消費類、無線鏈接和蜂窩基帶等。TSMC闡述了提供高級工藝來實現(xiàn)最低總功耗而不僅僅是靜態(tài)或者動態(tài)功耗的原因:

“我們之所以決定為28LPT工藝開發(fā)可靠的SiON技術,是因為無線和便攜式消費類應用需求在不斷變化,我們一直面對產(chǎn)品要符合市場需求的壓力。消費者幾年前需要低泄漏手持式設備,要求電池能夠使用較長的時間。今天的消費者越來越依靠無線設備來瀏覽互聯(lián)網(wǎng),觀看視頻,聽音樂,使用移動電視、GPS導航,以及傳統(tǒng)的電話和文本服務等。主動應用功耗現(xiàn)在是電池使用時間的主要因素。SiON邏輯門技術由于具有較小的柵極電容,因此,動態(tài)功耗比HKMG (高K金屬門)低,對于功耗受限的應用,提供的解決方案具有較低的總功耗,成本和風險也很低。”

28LP工藝具有較低的柵極電容,有源柵極電容比28HPL低30%。在Cyclone V和Arria V器件中,Altera還采用了其他方法來降低器件電容,包括用于存儲器控制器的硬核IP、PCI Express,還提供收發(fā)器協(xié)議支持,減小了管芯面積及其相關電容。最后,與Stratix V器件相比,Altera還針對Cyclone V和Arria V器件的基本體系結構模塊進行了優(yōu)化。這些優(yōu)化措施減小了硅片面積以及相關的電容,使得28LP器件系列滿足了目標應用的性能要求。例如,Arria V器件邏輯陣列模塊(LAB,10個自適應邏輯模塊)的管芯面積比Stratix V LAB小40%。Cyclone V和Arria V器件的硬核存儲器控制器也同樣減小了管芯面積以及外部存儲器接口的相關電容。所有減小器件電容的這些措施都降低了動態(tài)功耗,符合下面熟悉的功耗公式,其中,C表示開關電路的電容:

動態(tài)功耗 = 1/2CV 2 × f

Altera還降低了器件收發(fā)器的動態(tài)功耗。Altera豐富的收發(fā)器設計專業(yè)知識在業(yè)界是首屈一指的,其獨特的優(yōu)勢反映在收發(fā)器較低的動態(tài)功耗上。例如,在6 Gbps,Arria V收發(fā)器功耗不到100mW,比28-nm競爭FPGA的功耗低得多,如85C結溫,6 Gbps時每通道的收發(fā)器總功耗所示。對于采用了36個收發(fā)器Arria V器件的設計,功耗降低了5W多。

Altera在28-nm節(jié)點實現(xiàn)了較低的收發(fā)器功耗,這是因為我們經(jīng)過了多年的磨煉,增強了專用體系結構。在可編程邏輯業(yè)界,只有我們能夠持續(xù)不斷的發(fā)展高級收發(fā)器技術,因此,功耗一直在逐步降低。競爭解決方案每一代產(chǎn)品的收發(fā)器功耗都在增加,如所示,畫出了收發(fā)器物理介質(zhì)附加層(PMA)功耗與多代FPGA之間的關系曲線。

評論