安森美電路保護(hù)及濾波技術(shù)透視暨智能手機(jī)典型應(yīng)用示例

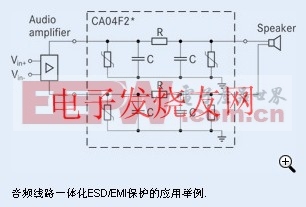

靜電放電(ESD)保護(hù)及電磁干擾(EMI)正在成為所有電氣設(shè)備越來(lái)越重要的考慮因素。消費(fèi)者要求智能手機(jī)等便攜/無(wú)線設(shè)備具有更多功能特性及采用纖薄型工業(yè)設(shè)計(jì),這就要求設(shè)計(jì)人員要求更加注重小外形封裝之中的ESD及EMI性能。本文將分析電路保護(hù)要求,比較不同的電路保護(hù)技術(shù)及濾波技術(shù),介紹安森美半導(dǎo)體應(yīng)用于典型電路保護(hù)及濾波應(yīng)用的產(chǎn)品,幫助設(shè)計(jì)工程師設(shè)計(jì)出更可靠的便攜及消費(fèi)類產(chǎn)品。

本文引用地址:http://www.104case.com/article/133535.htm關(guān)鍵芯片組外部ESD保護(hù)要求

業(yè)界正在采用最先進(jìn)的技術(shù)制造先進(jìn)的系統(tǒng)級(jí)芯片(SoC)。設(shè)計(jì)人員為了優(yōu)化功能及芯片尺寸,正在持續(xù)不斷地減小其芯片設(shè)計(jì)的最小特征尺寸。但相應(yīng)的代價(jià)是:隨著特征尺寸減小,器件更易于遭受ESD損傷。當(dāng)今的集成電路(IC)給保護(hù)功能所留下的設(shè)計(jì)窗口已經(jīng)減小。ESD保護(hù)必須在安全過(guò)壓及過(guò)流區(qū)工作。隨著業(yè)界趨向以更小幾何尺寸和更低電壓制造更先進(jìn)IC,IC的安全工作區(qū)也在縮小。

有效ESD保護(hù)的關(guān)鍵是限制ESD事件期間的電壓,令其處于給定芯片組的安全電壓窗口內(nèi)。ESD保護(hù)產(chǎn)品實(shí)現(xiàn)有效ESD保護(hù)的方式,是在ESD事件期間提供接地的低阻抗電流路徑;用于新集成電路的保護(hù)產(chǎn)品需要更低的動(dòng)態(tài)阻抗(Rdyn),從而避免可能導(dǎo)致?lián)p傷的電壓。

由于給保護(hù)功能所留的設(shè)計(jì)窗口減小,選擇具有低動(dòng)態(tài)阻抗的ESD保護(hù)產(chǎn)品變得更加重要,以此確保鉗位電壓不超過(guò)新芯片組的安全保護(hù)窗口。因此,ESD保護(hù)產(chǎn)品供應(yīng)商必須提供保護(hù)產(chǎn)品有效性的信息,而非僅是保護(hù)產(chǎn)品自身的存續(xù)等級(jí)。

硅ESD保護(hù)技術(shù)與無(wú)源ESD保護(hù)技術(shù)比較

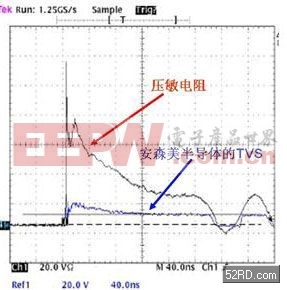

安森美半導(dǎo)體的保護(hù)及濾波方案基于先進(jìn)的硅工藝。相比較而言,其它幾種低成本無(wú)源方案結(jié)合使用了陶瓷、鐵氧體及多層壓敏電阻(MLV)材料。這些類型器件傳統(tǒng)上ESD鉗位性能較弱。在某些無(wú)源方案中,下游器件會(huì)遭受的電壓比安森美半導(dǎo)體硅方案高出一個(gè)或多個(gè)數(shù)量級(jí),下圖中的ESD屏幕截圖所示,其中比較了安森美半導(dǎo)體硅方案與競(jìng)爭(zhēng)技術(shù)在8 kV ESD應(yīng)力條件下的表現(xiàn)。競(jìng)爭(zhēng)技術(shù)的導(dǎo)通電壓如此之高,以致于它根本不會(huì)激活,所測(cè)的電壓只不過(guò)是在50 Ω測(cè)量電路上的電壓降。其它一些更老技術(shù)甚至在經(jīng)歷較少幾次ESD沖擊后性能就會(huì)下降。由于材料成分原因,某些無(wú)源器件往往在不同溫度條件下的性能表現(xiàn)不一致,因此在惡劣環(huán)境下的可靠性更低。

消除信號(hào)完整性問(wèn)題的PicoGuard® XS ESD保護(hù)技術(shù)

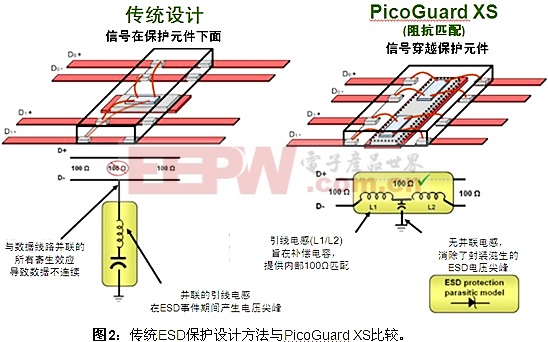

傳統(tǒng)ESD保護(hù)產(chǎn)品貼裝在信號(hào)走線與地之間,在信號(hào)路徑上不會(huì)產(chǎn)生中斷。為了將高速數(shù)據(jù)線路的信號(hào)完整性下降問(wèn)題減至最輕,電容必須最小化,如圖2所示。

評(píng)論