具有抗混疊濾波器和184.32 MSPS采樣速率的高性能65 MHZ帶寬四通道中頻接收機

抗混疊濾波器是采用標準濾波器設計程序(本例中是Agilent ADS)設計的四階巴特沃茲低通濾波器。選擇巴特沃茲濾波器是因為它具有平坦響應。四階濾波器產生1.03的交流噪聲帶寬比。其他濾波器設計程序可從Nuhertz Technologies 或Quite Universal Circuit Simulator (Qucs) Simulation 獲得。

本文引用地址:http://www.104case.com/article/131809.htm為了實現最佳性能,ADL5565應載入至少200 Ω的凈差分負載。20 Ω串聯電阻將濾波器電容與放大器輸出隔離開,當加入下游阻抗時可產生249 Ω的凈負載阻抗。

15 Ω電阻與ADC輸入串聯,將內部開關瞬變與濾波器和放大器隔離開。110 Ω電阻與ADC并聯,用于降低ADC的輸入阻抗,使性能更具可預測性。

AD6657A的差分輸入阻抗與2.2 pF并聯,約為2.4 kΩ。對于該類型的開關電容輸入ADC,實部與虛部與輸入頻率成函數關系;詳細分析請參見應用筆記AN-742。

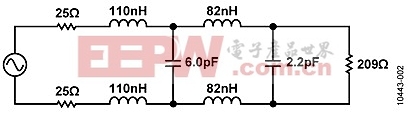

四階巴特沃茲濾波器采用50 Ω的源阻抗、209 Ω的負載阻抗和190 MHz的3 dB帶寬設計而成。濾波器的最終電路值如圖1所示。從濾波器程序生成的值如圖2所示。為濾波器無源元件選擇的值是最接近程序生成值的標準值。ADC的內部2.2 pF電容用作濾波器設計的最終分流電容。

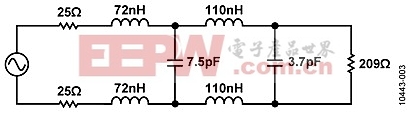

從本設計可以看出,最佳性能的獲得有時可以是迭代過程。濾波器程序設計值非常接近最終值,但由于存在一些板寄生電容,濾波器最終值略有不同。圖3顯示了濾波器的最終設計值。

圖2. 四階差分巴特沃茲濾波器的濾波器程序初始設計,ZS = 50 Ω,ZL = 209 Ω,FC = 190

圖3. 四階差分巴特沃茲濾波器的最終設計值,ZS = 50 Ω,ZL = 209 Ω,FC = 190 MHz

表1總結了系統的測量性能,其中3 dB帶寬為210 MHz。網絡的總插入損耗約為2 dB。圖4所示為最終濾波器電路的帶寬響應,圖5所示為SNR和SFDR性能。

評論