采用FemtoCharge技術(shù)的高速、高分辨率、低功耗的新一代ADC

先進(jìn)的系統(tǒng)架構(gòu)和集成電路設(shè)計(jì)技術(shù),使得模數(shù)轉(zhuǎn)換器(ADC)制造商得以開發(fā)出更高速率和分辨率,更低功耗的產(chǎn)品。這樣,當(dāng)設(shè)計(jì)下一代的系統(tǒng)時(shí),ADC設(shè)計(jì)人員已經(jīng)簡化了很多系統(tǒng)平臺的開發(fā)。例如,同時(shí)提高ADC采樣率和分辨率可簡化多載波、多標(biāo)準(zhǔn)軟件無線電系統(tǒng)的設(shè)計(jì)。這些軟件無線電系統(tǒng)需要具有數(shù)字采樣非常寬的頻率范圍,采樣高動(dòng)態(tài)范圍信號的能力,以同步接收遠(yuǎn)、近端發(fā)射機(jī)的多種調(diào)制方式的高頻信號。同樣,先進(jìn)的雷達(dá)系統(tǒng)也需要提高ADC采樣率和分辨率,以改善靈敏度和精度。在滿足了很多應(yīng)用的具體需求,ADC的主要性能有了很大提高的同時(shí),ADC的功耗也有數(shù)量級的下降,進(jìn)一步簡化了系統(tǒng)散熱設(shè)計(jì)和實(shí)現(xiàn)更小尺寸產(chǎn)品的設(shè)計(jì)。

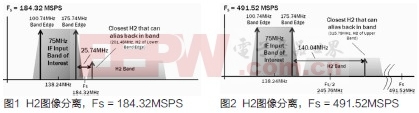

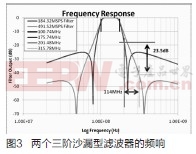

本文引用地址:http://www.104case.com/article/129007.htm在通信應(yīng)用領(lǐng)域,采用單個(gè)ADC數(shù)字化整個(gè)頻段,而不是有限數(shù)量的信道,可簡化接收機(jī)設(shè)計(jì)。為此,整個(gè)頻段必須在ADC的一個(gè)奈奎斯特區(qū)覆蓋范圍內(nèi),也就是說,采樣率(Fs)必須至少是有效頻譜帶寬(BW)的兩倍(FS ≥ 2*BW)。然而采用更高的采樣率可簡化抗混疊濾波器和接收機(jī)前級的設(shè)計(jì)。例如,采用184.32Msps采樣率加高選擇性濾波器可以數(shù)字化整個(gè)75MHz GSM頻段。濾波器限制在三階,要求ADC的二次諧波失真(H2)要優(yōu)于-75dBc。如圖1所示,上限帶邊至混疊回來的第一個(gè)干擾諧波的頻率間隔僅為25.74MHz。如果采樣率提高到491.52Msps,如圖2所示,最近處的混疊鏡像可移至距帶邊140.04MHz處,從而減輕濾波器和驅(qū)動(dòng)器組合的要求。圖3所示為兩個(gè)假定的三階沙漏型濾波器的頻響。在491.52Msps的情況下,干擾至帶邊的頻率間隔增加114MHz,這樣濾波器的設(shè)計(jì)更簡單,可采用更平緩衰減的濾波器,可以使用二次諧波性能指標(biāo)小于23.5dB的低功耗ADC驅(qū)動(dòng)器。

評論