引領28nm FPGA“智”造時代

Zynq-7000產品系列,集基于ARM Cortex-A9 MPCore處理器的完整片上系統(SoC)和集成28nm可編程邏輯為一體,專為要求高處理性能的嵌入式系統而構建,其目標市場包括汽車駕駛員輔助、智能視頻監控、工業自動化、航空航天與軍用、廣播以及新一代無線應用等。

本文引用地址:http://www.104case.com/article/127380.htmISE 13提升效率

當今芯片的架構設計/平臺成為必然,包括芯片和軟件兩部分,軟硬結合是架構設計最主要的特征。因此,7系列的推出也伴隨著軟件開發環境的創新。

賽靈思ISE Design Suite 13設計套件,專門針對最新28nm 7系列FPGA,ISE 13致力于讓客戶最大限度地利用有限的時間和設計資源實現最大的生產力。

ISE 13在CORE Generator系統中提供了AXI(Advance extensible Interface,先進的可擴展接口)互聯支持,以構建性能更高的點對點架構。設計團隊如果構建了自己的符合AXI協議的IP(知識產權),那么就能利用可選的AXI BFM(總線功能模型)驗證IP仿真AXI互聯協議,從而可輕松確保所有接口處理都能正確運行。賽靈思ISE 13還為設計人員帶來了強大的PlanAhead設計環境和分析工具。

堆疊硅片互聯:FPGA邁向3D

超越摩爾定律

長期以來,摩爾定律因其驚人的準確性,成為半導體行業發展的準則和軌跡。但是,單單依靠摩爾定律,可控的功耗和代工廠良率無法滿足市場對資源無止境的需求。為此,賽靈思找到了一個新的思路—堆疊硅片互聯(SSI)技術,加上與伙伴合作的技術/工藝,使賽靈思成為挑戰3D(三維封裝)FPGA的先鋒,可以為市場推出一種能夠應對當下挑戰的可行的可編程解決方案。

2011年10月,賽靈思橫空出世了堪稱世界最大容量FPGA—Virtex-7 XC7V2000T,為業界首批堆疊硅片架構的FPGA產品,其包含68億個晶體管,共200萬個邏輯單元(相當于2000萬個ASIC門)。據賽靈思公司全球高級副總裁、亞太區執行總裁湯立人介紹,Virtex-7 XC7V2000T不僅僅是晶體管數最大的FPGA產品,同時也是截至目前半導體歷史上集成晶體管數最多的單個IC—這不僅僅是摩爾定律的延續,更是對摩爾定律的超越。

因此,3D FPGA有望在一些領域內逐步取代ASIC和ASSP。湯立人稱,Virtex-7 2000T FPGA標志著賽靈思創新和行業協作史上的一個重大里程碑。對于客戶而言,其重大意義在于如果沒有SSI技術,至少要等演進到下一代工藝技術,才有可能在單個FPGA中實現如此大的晶體管容量。現在,有了Virtex-7 2000T FPGA,客戶能立即為現有設計增添新的功能,不必采用ASIC,單個FPGA解決方案就能達到3~5個FPGA解決方案的功能,因而可大幅降低成本。或者現在就可以開始采用賽靈思的最大容量FPGA進行原型設計和構建系統仿真器。這和通常的更新換代速度相比,至少可以提前一年時間。

SSI技術

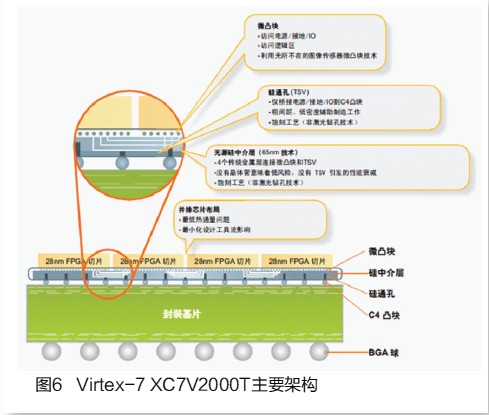

新的SSI技術使賽靈思能夠為當代工藝技術帶來下一代的高密度性能,有望改善容量和集成度,節約PCB(印制電路板)板級空間,進一步提高產量。Virtex-7 XC7V2000T主要架構如圖6所示。

1. FPGA核心

最上層為FPGA核心層,采用4個含50萬邏輯單元的28nm FPGA核心(切片)肩并肩排布,而非采用2個含100萬邏輯單元的或單個200萬邏輯單元的FPGA核心。原因在于當IC的規模和復雜度不斷提升的同時,其良品率將受到一定程度的影響。此種設計能在保證良品率的同時,提高邏輯單元數目。

2. 微凸塊

微凸塊并非直接連接于封裝,而是互聯到SSI技術最關鍵的部分——無源硅中介層,進而連接到相鄰的芯片。這種設置方法能夠避免微凸塊受到靜電放電的影響,從而帶來巨大優勢。通過芯片彼此相鄰,并連接至球形柵格陣列,該器件避免了采用單純的垂直硅片堆疊方法出現的熱通量、信號完整性和設計工具流問題。

3. 硅中介層

SSI技術設置了一個65nm工藝的無源硅中介層,其本質類似于IC內部的互連線,在芯片外部實現了芯片間的直接互聯。這樣解決了傳統方式所帶來的問題,將單位功耗芯片間連接帶寬提升了100倍以上,時延減至五分之一,也不會占用任何高速串行或并行I/O資源。而且,硅片中的芯片連接數量大大超過系統級封裝。而且這種方法的最大優勢還在于節能性。通過SSI技術連接芯片,其功耗遠遠低于通過大線跡、封裝或電路板連接的方式。

評論