引領(lǐng)28nm FPGA“智”造時(shí)代

2010年,TSMC已為客戶(hù)的28nm FPGA提供了先進(jìn)的硅穿孔(TSV, Through Silicon Via)以及硅中介層(Silicon Interposer)的芯片驗(yàn)證(prototyping) 服務(wù)。憑借TSMC研發(fā)的TSV及與IC制造服務(wù)業(yè)者兼容的晶圓級(jí)封裝技術(shù),TSMC承諾與客戶(hù)緊密合作開(kāi)發(fā)符合成本效益的2.5D/3D(2.5維/3維)集成電路系統(tǒng)整合方案。

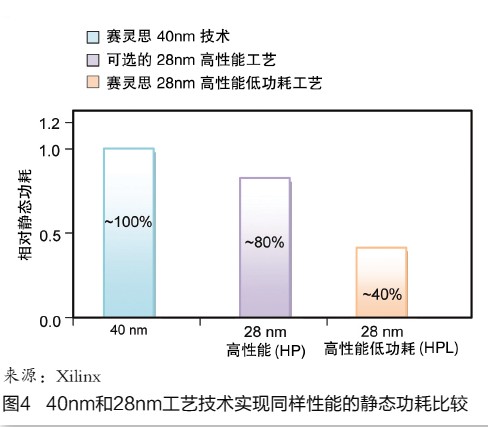

本文引用地址:http://www.104case.com/article/127380.htm如果用一個(gè)簡(jiǎn)單的量化標(biāo)準(zhǔn)來(lái)衡量28nm和40nm工藝的區(qū)別的話,集成度是傳統(tǒng)40nm工藝的兩倍。通過(guò)將更多功能單元集成在單一的系統(tǒng)級(jí)芯片上,企業(yè)可以大幅降低終端產(chǎn)品成本,并且可以制造出更小、更薄的產(chǎn)品。與傳統(tǒng)的40nm工藝相比,在指定速度下,28HPL的功耗最高可以減少一半(圖4),部分設(shè)計(jì)的待機(jī)功率更可以低至30%,而速度上最高可以有將近80%的提升。

賽靈思的全新FPGA就是基于TSV技術(shù)的28nm新產(chǎn)品,賽靈思亞太區(qū)銷(xiāo)售及市場(chǎng)副總裁楊飛坦言這得益于28nm工藝技術(shù)——28nm高性能低功耗工藝(28HPL)。賽靈思推出了統(tǒng)一的Virtex架構(gòu),將整體功耗降低一半且具有高容量(200萬(wàn)邏輯單元)的7系列FPGA產(chǎn)品,不僅能實(shí)現(xiàn)出色的生產(chǎn)率,解決 ASIC 和 ASSP 等其他方法開(kāi)發(fā)成本過(guò)高、過(guò)于復(fù)雜且不夠靈活的問(wèn)題,使 FPGA 平臺(tái)能夠滿(mǎn)足日益多樣化的設(shè)計(jì)群體的需求。

設(shè)計(jì)挑戰(zhàn)

新工藝帶來(lái)新競(jìng)爭(zhēng)優(yōu)勢(shì)的同時(shí),將許多設(shè)計(jì)和制造上的挑戰(zhàn)也帶給業(yè)界,為此,要求設(shè)計(jì)者與EDA(電子設(shè)計(jì)自動(dòng)化)和晶圓廠之間保持良好的合作以應(yīng)對(duì)全新的設(shè)計(jì)和制造挑戰(zhàn)。

談及SoC(系統(tǒng)級(jí)芯片)設(shè)計(jì)師在新的節(jié)點(diǎn)中將會(huì)遇到的工具和方法的轉(zhuǎn)變, Synopsys公司戰(zhàn)略聯(lián)盟總監(jiān)Kevin Kranen認(rèn)為,新節(jié)點(diǎn)面臨的挑戰(zhàn)各不相同:32nm和28nm的EDA工具需求相同,其所面臨的主要挑戰(zhàn)包括以下幾方面:

⒈由于SiON柵極介質(zhì)厚度過(guò)薄難以控制,在降低柵極漏電和閾值變異性方面的挑戰(zhàn);

⒉在193nm光刻基本限值下的挑戰(zhàn);

⒊用于參數(shù)提取的新工藝拓?fù)浣Y(jié)構(gòu)建模方面的挑戰(zhàn);

⒋管理參數(shù)異變性,尤其是在簽核期間異變性的挑戰(zhàn)。

評(píng)論