FPGA與GPS_OEM板的UART設(shè)計(jì)

引言

本文引用地址:http://www.104case.com/article/123978.htmUART(標(biāo)準(zhǔn)異步接收器/發(fā)射器)得到了相當(dāng)廣泛的應(yīng)用,它允許串行鏈路上進(jìn)行全雙工通信。一般使用通用的UART接口芯片,但這種芯片存在電路復(fù)雜、成本高,降低了系統(tǒng)的可靠性和穩(wěn)定度,由于結(jié)構(gòu)和功能的相對固定,因而我們不能根據(jù)自己的設(shè)計(jì)需要去進(jìn)行剪裁和移植。而日益成熟的SOPC(Silicon on Programmable Chip,系統(tǒng)可編程芯片)技術(shù)要求將整個(gè)設(shè)計(jì)功能集成到一塊或幾塊芯片中,本文通過對UART功能的分析,提出了在FPGA上集成UART功能模塊,增強(qiáng)了設(shè)計(jì)的靈活性,簡化了電路,并通過有限狀態(tài)機(jī)來描述核心功能控制邏輯,從而提高了整個(gè)系統(tǒng)的穩(wěn)定性和可靠度。基于這種思想,本文提出了一種使用VHDL[1]語言開發(fā)UART核心功能的方法,將UART模塊嵌入到FPGA芯片,實(shí)現(xiàn)了FPGA與GPS_OEM板之間的數(shù)據(jù)通信,為FPGA采集并處理GPS_OEM板數(shù)據(jù)提供基礎(chǔ)。UART所有功能的實(shí)現(xiàn)全部采用VHDL硬件描述語言來進(jìn)行描述。設(shè)計(jì)、綜合、仿真在QUARTUS II9.0軟件開發(fā)環(huán)境下實(shí)現(xiàn)。

系統(tǒng)設(shè)計(jì)

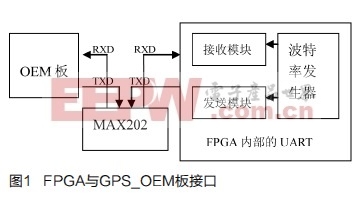

由于FPGA接口采用TTL電平,而OEM[2]板的串行通信采用RS-232標(biāo)準(zhǔn)電平,故需電平轉(zhuǎn)換,電平轉(zhuǎn)換接口可以通過MAX202[3]片來實(shí)現(xiàn)。GPS25LP[4]兩個(gè)串行口,其端口1可用來輸入差分修正信息和輸出衛(wèi)星的原始測量信息,而端口2則用來輸入設(shè)定語句和輸出定位語句,因此,只需將FPGA接口與GPS25LP串行口2對應(yīng)連接即可。其接口電路如圖1所示。FPGA的全局時(shí)鐘Global_clk由24 MHz的晶振產(chǎn)生。

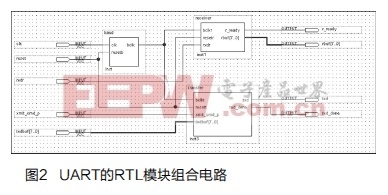

UART電路由波特率發(fā)生器、發(fā)送模塊和接收模塊3部分組成。UART的RTL(寄存器傳輸級)模塊組合電路如圖2。波特率發(fā)生器為發(fā)送模塊和接收模塊提供時(shí)鐘信號,以實(shí)現(xiàn)數(shù)據(jù)的異步可靠傳輸。

假定本方案設(shè)計(jì)的UART數(shù)據(jù)格式為:數(shù)據(jù)位為8位、波特率可選、不設(shè)奇偶校驗(yàn)位、1位停止位,異步通信的過程如下:GPS_OEM板產(chǎn)生發(fā)送串行數(shù)據(jù),由MAX202的TXD端輸入,經(jīng)過MAX202進(jìn)行電平轉(zhuǎn)換由FPGA串口接收模塊的RXD端進(jìn)入,進(jìn)行串并轉(zhuǎn)換得到8位位寬數(shù)據(jù)總線,該數(shù)據(jù)由FPGA的其他模塊進(jìn)行處理;FPGA產(chǎn)生發(fā)送的8位并行數(shù)據(jù),數(shù)據(jù)由8位數(shù)據(jù)線進(jìn)入FPGA串口發(fā)送模塊,進(jìn)行并串轉(zhuǎn)換后由TXD輸出到MAX202的,經(jīng)過MAX202電平轉(zhuǎn)換發(fā)送至GPS_OEM板。

fpga相關(guān)文章:fpga是什么

晶振相關(guān)文章:晶振原理

評論