FAE講堂:利用賽靈思FGPA實現降采樣FIR濾波器

本文引用地址:http://www.104case.com/article/119299.htm

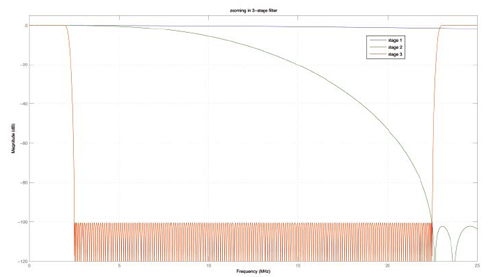

圖 3. 通過串聯三個FIR濾波級進行的按 50 整數抽取,此處單獨放大顯示0~25MHz頻率。

用于三級濾波器的FIR-Compiler設置與圖1及圖2所示大同小異。第一個濾波器唯一不同的參數是COE文件名和“抽取率值”,其分別設為filt1_rad10.coe和M1=2。第二個濾波器COE文件名是filt2_rad10.coe,抽取率值為M2=5,輸入采樣頻率此時為125MHz,因為第二級按M1=2抽取來自第一級的輸入數據。最后,第三個濾波器參數的唯一區別是COE文件名為filt3_rad10.coe,抽取率值為M3=5,輸入采樣頻率此時為25MHz,因為第三級按M2=5抽取來自第二級的輸入數據。

在布局布線后,三個濾波級占用以下FPGA資源:

第一級(M1=2):

Slice觸發器數量:280 個

Slice LUT數量:208 個

占用 Slice數量:62 個

DSP48 MAC單元數量:3個

第二級(M2=5):

Slice觸發器數量:236個

Slice LUT數量:168 個

占用 Slice數量:60 個

DSP48 MAC單元數量:3 個

第三級(M3=5):

Slice觸發器數量:357 個

Slice LUT數量:414 個

占用 Slice數量:158 個

DSP48 MAC單元數量:4 個

由于采用上述多級方法,我們現在比參考濾波器最初的22個DSP48 MAC單元少用了12個單元;與單級理想濾波器占用資源相比,我們節約了30%左右的觸發器,55%的LUT,44%的slice和54%的DSP48單元。

與CIC濾波器串聯

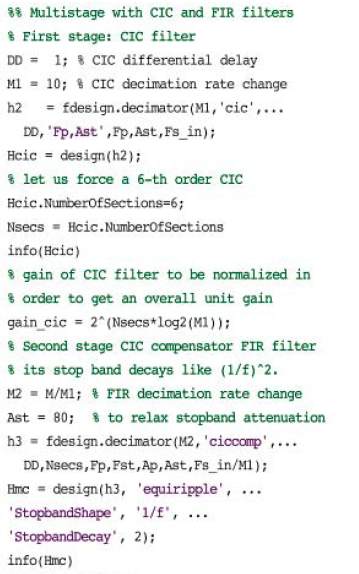

另一種按50抽取的可行方法是把級聯積分梳狀 (CIC) 濾波器 和CIC補償降采樣級串聯在一起,其變化速率分別為M1=10與M2=5。CIC濾波器是一類特殊的FIR濾波器,由N個梳狀濾波器和積分器組成(因此產生“第 N 級”術語)。盡管梳狀濾波器仍然可以實現成一種“傳統的”基于MAC的FIR濾波器,不過CIC架構之所以有趣是因為它不需要任何MAC單元,因此可以用CLB sclice替代DSP48單元,參閱CoreGen CIC-Compiler 1.3數據手冊(cic_compiler_ds613.pdf)。

按M1=10抽取的第一級CIC濾波器頻率響應較差,因此需要采用一個按M2=5抽取的補償FIR濾波器,以彌補第一級CIC濾波器本身通帶的下降。以下MATLAB代碼說明如何采用FDA工具設計此類濾波器。

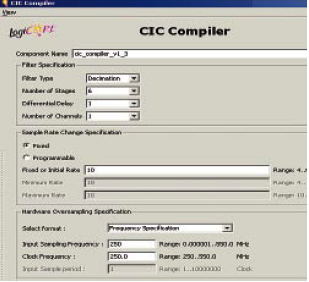

圖4為賽靈思CoreGen CICCompiler 1.3 GUI設置的第一個頁面;其它參數采用默認值,“使用Xtreme DSP Slice”可選參數除外(GUI 的第2頁(共3頁)),

圖 4. 按10抽取的CIC濾波器的設置。CIC-Compiler 1.3 GUI的第1頁(共 3 頁)。

其允許采用或不采用DSP48單元實現梳狀濾波器。FIR Compiler GUI中的CIC補償FIR濾波器設計參數與圖1及圖2所示相同;唯一不同的設置是 COE 文件名(此處是ciccomp_ dec5.coe),抽取率值為M2=5,而輸入采樣頻率為25MHz。

在布局布線后,兩個濾波級占用以下FPGA資源:

第一級(按10抽取的CIC濾波器,不使用“采用Xtreme DSP Slice”)

Slice 觸發器數量:755 個

Slice LUT 數量:592 個

占用 Slice 數量:172 個

DSP48 MAX 單元數量:0 個

第一級(按10抽取的CIC 波器,使用“采用 Xtreme DSP Slice”)

Slice 觸發器數量:248 個

Slice LUT 數量:154 個

占用 Slice 數量:42 個

DSP48 MAC 單元數量:7 個

第二級(按5抽取的CIC補償FIR濾波器)

Slice 觸發器數量:271 個

Slice LUT 數量:312 個

占用 Slice 數量:114 個

DSP48 MAC 單元數量:3 個

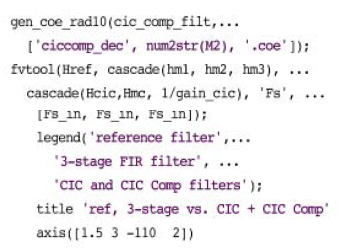

兩種結果都很有趣,而是否選擇使用Xtreme DSP slice取決于設計人員最需要節約哪些資源。我個人選擇“采用Xtreme DSP Slice”選項。與單級濾波器相比,我們可以節約大約59%的觸發器,73%的LUT,69%的slice和54%的DSP48 MAC單元。代價是阻帶衰減更差,其現在是80dB,而非所需要的100dB,如圖5所示。某項設計是否接受該衰減值事實上與應用相關。

濾波器相關文章:濾波器原理

濾波器相關文章:濾波器原理

電源濾波器相關文章:電源濾波器原理

評論