FAE講堂:利用賽靈思FGPA實現降采樣FIR濾波器

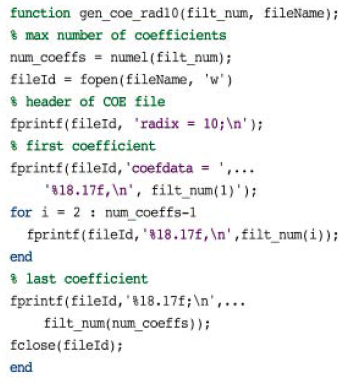

為了設計參考濾波器,CoreGen FIR-Compiler需要名為“COE 文件”的系數文本文件。以下MATLAB例程說明如何以十進制基數輕松生成此 COE 文件;FIR-Compiler 然后按照所采用的設置量化相關系數。

本文引用地址:http://www.104case.com/article/119299.htm

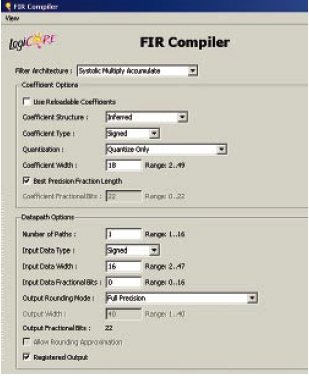

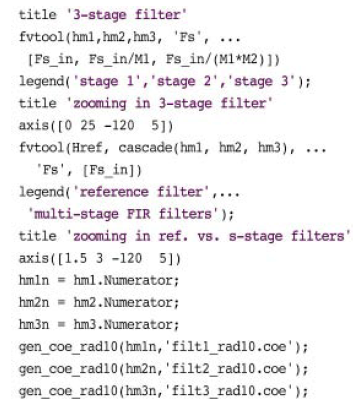

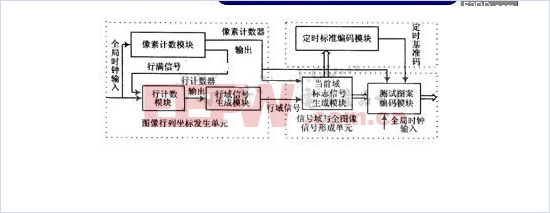

圖1與圖2說明FIR-Compiler GUI頭兩個頁面所應用的設計參數;在最后兩個頁面我只需接受其默認值,但是“優化目標 (Optimization Goal)”除外, 我把它設為“速度 (Speed)”而非“區域 (Area)”。如無明確說明,我在本文件以及下面例子中始終采用上述設置。在完成ISE 11.4布局布線之后,參考單級降采樣濾波器占用以下FPGA資源:

Slice觸發器數量:1,265 個

Slice LUT數量:1,744 個

占用的 Slice數量:502 個

DSP48單元數量:22 個

圖 1. 50整數降采樣。參考單級濾波器的FIR-Compiler 5.0 GUI設置第1頁(共4頁)。

圖 2. 50整數降采樣。參考單級濾波器的FIR-Compiler 5.0 GUI設置第2頁(共4頁)。

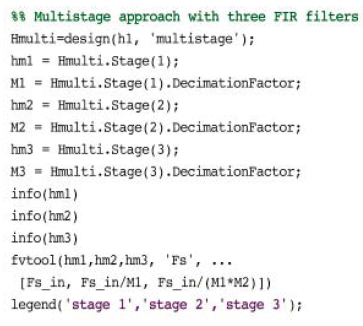

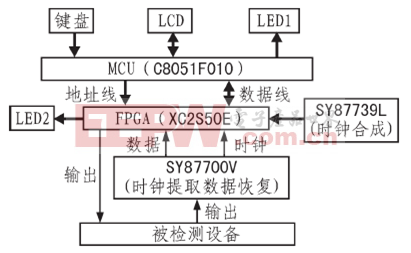

三個FIR濾波級串聯

現在我們以濾波級串聯方式實現理想抽取濾波器。這種方法可以讓我們通過時分復用節省MAC單元,因為每個新的濾波級都是按前一級提供的較低數據速率運行。我讓FDA工具決定最佳濾波類型:利用 MATLAB 指令信息,您可以看出:它會提出三級解決方案建議,其抽取因數分別是M1=2、M2=5和M3=5。

圖3顯示了組成上述多級系統的三個濾波器的頻率響應。藍色曲線代表第一個降采樣濾波器(M1=2);綠色曲線代表第二個濾波器 (M2=5),按Fs_in/M1倍數周期波動;而紅色曲線則代表第三個降采樣器 (M3=5),按Fs_in/(M1*M2)倍數周期波動。

濾波器相關文章:濾波器原理

濾波器相關文章:濾波器原理

電源濾波器相關文章:電源濾波器原理

評論