MIPS -- 適用于MCU的處理器

3.2 系統協處理器(CP0)

本文引用地址:http://www.104case.com/article/118393.htm系統協處理器(CP0)是MIPS架構所特有的,可以在M4K內核中找到。CP0作為輔助執行單元工作,可減少內核資源的某些管理操作(包括異常處理和存儲器管理),從而提高內核性能。

3.3 通用寄存器(GPR)和影子寄存器

M4K內核提供一個配置選項,可將GPR的數量增加到最多16組,且每組都有完整的32個寄存器。這些GPR可在片上存儲參數和操作數,從而減少存儲器轉移開銷并減少指令周期。這對增加計算吞吐量有著積極作用。

如前文所述,使用GPR作為影子寄存器可以減少服務中斷(MCU系統中的常見事件)所產生的開銷,從而提高系統性能。

當處理中斷或異常時,M4K內核會決定使用哪個影子寄存器組并使其成為激活的GPR組,以允許中斷向量繼續執行。此過程完全不需要現場保護或恢復周期,因為指定的中斷服務程序是當前激活的影子寄存器的唯一所有者。這意味著不僅在中斷或異常代碼實際開始執行前不會浪費時間,而且自上一次異常或中斷事件激活以來的寄存器內容都會被保留。這會節省從SRAM空間重新獲取特定值的時間。

3.4 MDU

M4K內核中的高性能MDU可在一個周期內完成一次32x16位乘法(或MAC指令)。在兩個周期內完成32x32位乘法/MAC運算。

MDU有自己的專用功能單元,可獨立于內核執行流水線進行工作。任何乘法/除法指令都會被送到MDU,這樣內核流水線可并行處理其他操作,例如需要ALU、加載/存儲和移位運算的指令。M4K內核中的MDU具有使信號處理運算加速的優勢,例如FFT、FIR和IIR這些在工業和網絡型應用中通常由單片機執行的濾波計算。以M4K加速DSP型函數的能力為例,PIC32在80MHz的頻率下運行256點的16位radix-4 FFT運算需要22K個周期,共花費283ms,比基于Cortex-M3的單片機STM32少用14%的周期。

3.5 SRAM接口

訪問代碼和數據的速度快慢對處理器性能有明顯影響。設計人員致力于設計一種存儲器接口,使可用帶寬最大化且最大程度地降低延遲,目標是實現0等待狀態的數據傳送。MIPS架構采用靈活的存儲器總線結構,允許從高速閃存或高性能片上SRAM中執行代碼。M4K內核集成了一個用于指令和數據存儲器的高速、低延時SRAM接口。該接口支持單周期和多周期存儲器訪問。M4K SRAM接口可工作在雙模式或統一模式下。雙模式提供最高的性能,并具有控制數據(D-SRAM)和指令(I-SRAM)的獨立總線。雙模式允許在I-SRAM和D-SRAM接口上同時執行數據傳輸,以消除公用總線接口上可能產生的沖突現象。

I-SRAM接口能夠重新定向信號輸入,必要時允許將D-SRAM讀周期重新定向到I側。這樣便可實現改良的哈佛架構(這是基于MCU的系統的常規特性),允許將非易失性數據存儲在程序存儲器中。

SRAM接口可在M4K內核的5級流水線中的任意位置中止指令事務。這樣便可從外部系統控制器對外部事件(例如中斷請求或通過EJTAG調試接口發出的請求)做出立即響應。在處理典型單片機應用的高決定性操作時,對外部中斷事件的快速響應至關重要。

SRAM接口還可中止延時較長的數據傳輸。在處理典型單片機應用的高決定性操作時,對外部中斷事件的快速響應至關重要。

M4K內核中的SRAM接口是一個高速、易用且可靈活配置的存儲器接口,其中大多數傳輸可在一個時鐘周期內完成。它除處理指令和數據存儲器之外不會產生任何額外的協議或信號開銷,這使芯片設計人員可充分利用M4K內核的最大性能。

Cortex-M3則沒有如此全面的存儲器控制功能,因此在性能上不如M4K內核。

3.6 CorExtend™

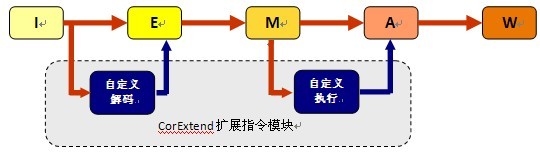

CorExtend是MIPS32架構的另一個獨特功能,它為開發人員提供了產品差異化和定制功能。它是一個配置選項,通過用戶定義指令(User Defined Instructions,UDI)與定制硬件的結合來擴展內核指令集。設計人員可通過CorExtend為內核增加功能,在目標應用中對成為瓶頸的特定應用功能進行加速,從而提高系統的整體性能。在典型MCU環境中,CorExtend可用于設計專用圖形控制器、TCP/IP加速器、定制安全/加密邏輯、無線基帶控制或其他實時控制接口等。CorExtend與內核流水線協同工作,如圖3所示。CorExtend的功能與MIPS32完全兼容,并且所有領先的MIPS兼容開發工具均能支持。

圖3:CorExtend流水線結構

4.性能基準測試

CoreMark是EEMBC開發的開源基準測試工具,專為測試處理器內核的性能而設計。CoreMark的架構可將處理器內核與任何相關系統隔離,包括存儲器子系統的影響以及編譯器可能使出的“優化把戲”。CoreMark可測試處理器流水線以及常用功能(包括讀/寫、整數和控制操作)的性能。因此,它提供的測試結果中的人為影響要比其他基準測試少,更接近處理器內核的真實性能。

源自CoreMark網站所述:“測試內容實際由多個常用算法組成,包括矩陣操作(允許使用MAC和常用數學運算)、鏈表操作(執行指針的常規用途)、狀態機操作(數據相關分支的常規用途)以及循環冗余校驗(CRC是嵌入式應用中很常用的功能)”。

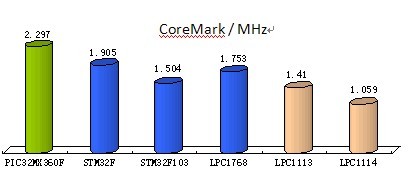

圖4比較了一些基于MIPS M4K和ARM Cortex-M3及M0的MCU的數據,這些數據取自CoreMark公開網站。

圖4:M4K PIC32與ST和NXP Cortex-M器件的CoreMark比較結果

工作在80MHz下的M4K PIC32采用2等待狀態的存儲器,其性能優于競爭對手的采用0等待狀態存儲器的Cortex-M3和M0器件,具體數據為:

比工作在120MHz下的STM32F高20%

比工作在72MHz下的STM32F高50%

比工作在100MHz下的LPC1768高31%

比工作在50MHz下的LPC1113高63%

評論