一種多體制通信時間同步算法及其FPGA實現

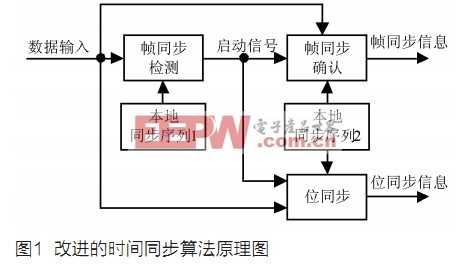

幀同步確認

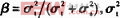

本文引用地址:http://www.104case.com/article/116957.htm幀同步確認的主要目的是判斷幀同步檢測結果是否屬于假同步,減少出現假同步的概率。它利用接收同步序列的后半部分與本地同步序列的后半部分(即圖1中的本地同步序列2)之間的相關性實現。由于幀同步確認時,位同步、載波同步等模塊同時工作,幀同步確認受載波頻偏等因素的影響較小,可以采用接收序列與本地序列直接相關的算法實現。

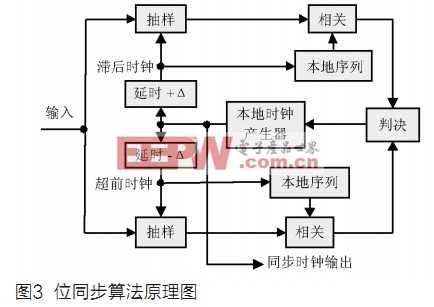

位同步

位同步模塊在幀同步檢測成功后啟動(與幀同步確認同時進行),利用接收同步序列的后半部分與本地同步序列的后半部分(即圖1中的本地同步序列2)之間相關性,通過利用比較時鐘與接收碼元之間的相關差來判斷本地時鐘是否需要進行調整,從而實現位同步。當最佳判決點處于接收信號碼元的中間位置時,位同步算法原理如圖4示,其中超前時鐘和滯后時鐘作為比較時鐘。對于最佳判決點不處于碼元中間的情況,只要修改圖3中超前、滯后時鐘與本地時鐘之間的相位差即可。

相關器采用與幀同步檢測相同的相關方法式(1):當最佳判決點處于碼元中間的情況,即本地時鐘相位與最佳判決點一致時,超前時鐘和滯后時鐘相位都在最佳判決點附近,其相關結果基本相同,本地時鐘產生器不需要進行調整;當本地時鐘相位超前于最佳判決點時,超前時鐘遠離最佳判決點,其控制下相關器的輸出減小為(P1-1)/2,而滯后時鐘控制下相關器的輸出仍為(P1-1),判決模塊通知本地時鐘產生器進行滯后處理。同理,當本地時鐘相位滯后于最佳判決點時,產生器進行超前處理。

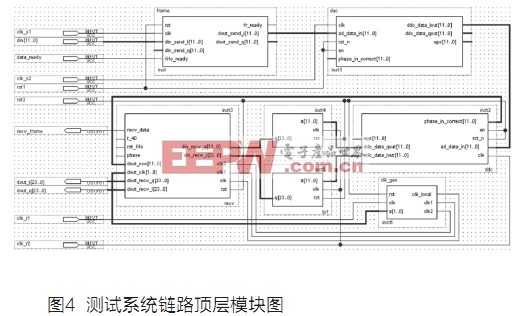

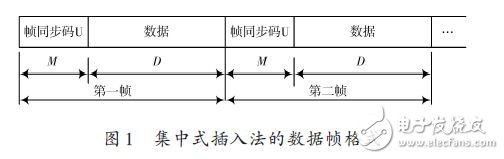

FPGA實現與仿真驗證

根據新一代無線通信統一平臺的特點,同步功能需要在FPGA內實現。本文利用Altera的quartus設計軟件,采用自頂向下的模塊化設計方法,用VHDL語言完成時間同步相關的各個模塊的編程設計,并利用仿真軟件modelsim完成仿真驗證。測試系統如圖5。其中,發端主要包括成幀(frame)和上變頻(duc)兩個模塊,將信源數據按一定標準組成幀,并調制到一定的中心頻率發出;收端主要包括下變頻(ddc)、低通濾波(lpf)、時鐘生成(clk_gen)和同步處理(recv)等模塊。其中,recv包含了幀同步、位同步和載波同步等模塊,duc和ddc模塊為了測試存在載波頻偏時的同步算法性能而加入。

評論