一種多體制通信時間同步算法及其FPGA實現

幀同步檢測

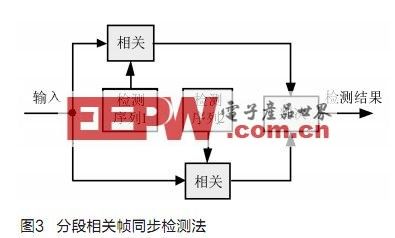

本文引用地址:http://www.104case.com/article/111962.htm根據文獻[2],基于互相關的幀同步算法對載波頻偏的容忍度與本地同步序列的長度成反比。所以,為了進一步減少幀同步的漏同步概率,在將本地同步序列分成幀同步檢測和幀同步確認兩部分的基礎上,本文的幀同步檢測采用如圖3所示的分段相關法[6]。在分段相關的幀同步檢測算法中,用于幀同步檢測的本地同步序列1等分為檢測序列1和檢測序列2兩段,然后用這兩段檢測序列同時與輸入信號進行相關,只要一個相關結果大于門限,就認為幀同步檢測成功。

為了使幀同步算法更適于在FPGA中實現,本文對傳統相關器進行了改進,實現方法如下:

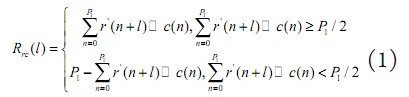

首先對接收信號進行抽樣判決(即將大于0信號的判決為“1”,否則判決為“0”),將接收信號變換為由“0”和“1”組成的序列,然后再與用于本地同步序列(用于幀同步檢測的本地同步序列)進行相關運算。其中,相關函數可以定義為:

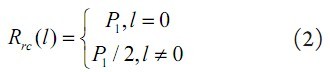

其中,表示同或,表示同步序列長度。考慮到接收信號中的數據塊與本地同步序列c(n)無關,并忽略噪聲的影響,可以得到:

即,只有在時,出現相關峰。

使用上述相關方法,載波頻偏引起的接收信號幅度變化不會影響相關峰幅度,只有在頻偏引起接收抽樣序列在發生反相時,相關結果小(如當在中間位置反相時,前半段相關結果為,后半段相關結果為0,從而導致)。而由于本文的幀同步檢測使用分段相關的方法,通常情況下載波頻偏引起接收同步序列在每個分段都產生反相的可能性很小,所以可以有效防止載波頻偏引起漏同步發生的概率。

幀同步確認

幀同步確認的主要目的是判斷幀同步檢測結果是否屬于假同步,減少出現假同步的概率。它利用接收同步序列的后半部分與本地同步序列的后半部分(即圖2中的本地同步序列2)之間的相關性實現。由于幀同步確認時,位同步、載波同步等模塊同時工作,幀同步確認受載波頻偏等因素的影響較小,可以采用接收序列與本地序列直接相關的算法實現。

數字通信相關文章:數字通信原理

通信相關文章:通信原理

評論