多功能數據采集處理系統實現

DSP總線接口設計

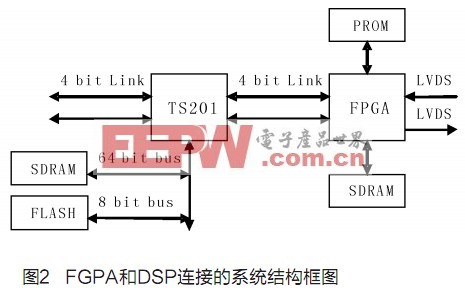

本文引用地址:http://www.104case.com/article/110979.htmADSP TS201外部總線支持多種不同的協議,并且可以通過編程進行配置。外部總線接口支持流水線協議,SDRAM協議和慢速設備協議。TS201可以采用流水線協議訪問存儲系統。另外TS201有片上的SDRAM控制器,支持與SDRAM的無縫連接。本設計中總線上的外設分別為SDRAM以及DSP加載程序的FLASH存儲器。

TS201處理器的SDRAM接口,支持1024、512、256字的頁面長度,通過對SDRCON 寄存器的編程可實現頁面長度的選擇。同時SDRAM占用TS201的外部存儲空間地址,通過/MSSD3~0來確定SDRAM的地址空間范圍。本設計選用的SDRAM型號為K4S511632M,頁面長度為512字,將四片SDRAM拼接成64位的總線寬度,實現與TS201的無縫接口的256MB存儲空間。

DSP進行運算除了其外部存儲器外,還需要對其自身進行程序加載的BOOT FLASH。本設計中使用AT49BV321,設計中FLASH的CE信號需要使用DSP的BMS和MS0 相與后給入,這樣才能保證可以通過DSP的外總線給FLASH進行在線編程。

系統應用

本文設計的高速數據采集與處理系統,借助上面介紹的硬件平臺,可以完成通用的數據采集與處理,其中關鍵的問題就是后續的處理系統設計,即后續的信號處理系統完成的算法與功能。針對輸入信號的不同以及高速數據采集與處理系統的用途,后續的信號處理算法也具有多樣性。

數字下變頻

對于接收通道送來的中頻信號,由于本系統采用了105Msps的采樣率,故可以直接采樣后進行下變頻處理,如圖3所示。數字下變頻器的組成包括數字混頻器、數字控制振蕩器和低通濾波器,全部可以在FPGA中實現,因為通過軟件進行運算,乘法器和低通濾波器可以做到完全一致,解決了I、Q通道幅度不平衡的問題,數字下變頻器的控制和修改也更加容易。

脈壓

在雷達回波信號處理中,通常利用線性調頻信號脈沖壓縮技術來獲得高的距離分辨率,它可以在保證雷達作用距離的情況下提高雷達的距離分辨率。數字脈沖壓縮就是利用數字信號處理的方法來實現雷達信號的脈沖壓縮,分為時域和頻域兩種實現方式。一般而言,對于小時寬帶寬積信號,用時域脈壓較好,可以用專用的FIR濾波器或FPGA設計實現;但對于大時寬帶寬積信號,用頻域脈壓較好,一般采用FFT方法在頻域實現。由于DSP芯片具有很強的數據處理能力,完全能夠滿足雷達脈沖壓縮信號處理實時性的需求。

動目標檢測(MTD)

MTD是根據最佳濾波器理論發展起來的一種雷達信號處理技術。MTD濾波器是一組相鄰且部分重疊的窄帶濾波器組,覆蓋整個重復頻率的范圍。由于固定雜波和運動目標回波的多譜勒頻移不相同,利用多譜勒濾波器濾去固定雜波而取出運動目標的回波,就可以大大改善在雜波背景下檢測運動目標的能力。采用加權法的每個濾波器具有較低的副瓣,可以抑制運動雜波,還有在零頻附近的深凹口抑制固定雜波,具有較好的雜波抑制性能。MTD利用DSP內部的FFT運算實現相參積累,不但提高了系統輸出的信噪比,還增強了雷達在各種雜波以及干擾條件下的目標檢測能力。

上面舉了一些應用方面的例子,諸如MTI、CFAR、積累、求模以及目標錄取之類的應用,在本系統中也可以輕松地實現。

結語

本文提出了一種基于FPGA和DSP的高速數據采集處理系統設計方案。該設計具有一定的通用性和可擴展性,FPGA可完成高速數據的存儲與相應的數據預處理,為DSP分擔部分信號處理工作,且硬件實現速度快于DSP的數據處理;采用浮點DSP進行后續處理,提高了數據處理精度。該高速數據采集處理系統可以通過修改FPGA內部程序來實現其它功能擴展,并利用后續DSP的強大實時處理能力,完成更為復雜的數字信號處理,因此在工程應用上具有較強的通用性。

參考文獻

[1] 劉書明,蘇濤, 羅軍輝.TigerSHARC DSP應用系統設計[M].北京:電子工業出版社,2004

[2] AD 公司TigerSHARC DSP 系列數據手冊- ADSP2TS201S 部分

[3] 吳繼華,王誠. Altera FPGA/ CPLD 設計[M] . 北京:人民郵電出版社,2005 :53 - 88

[4] 廖日坤. CPLD/ FPGA 嵌入式應用開發技術白金手冊[M] . 北京:中國電力出版社,2005 :18 - 46

[5] 蘇濤,吳順君,廖曉群. 高性能數字信號處理器與高速實時信號處理[M] . 西安:西安電子科技大學出版社,2002

[6] 楊小牛, 樓才義, 徐建良. 軟件無線電原理與應用[M] . 北京:電子工業出版社, 2001

評論