多功能數據采集處理系統實現

A/D電路

本文引用地址:http://www.104case.com/article/110979.htm高速A/D芯片的輸入端通常采用差分輸入,這種方式有以下優點:差分特性對來自電源和其他電路的外部共模噪聲源具有抑制作用;能夠抵消偶次諧波;每個差分輸入所需電壓擺幅僅為單端輸入時的50%,可以降低對電源的要求。

本設計中運放采用的是ADI公司的AD8138,體積非常小巧,使得A/D芯片與信號輸入點的距離可以很近,大大減少了外界噪聲的影響,是理想的驅動芯片。單端轉差分器件選用Mini-Circuits 公司的寬帶變壓器ADT1-1WT,其工作頻帶為0.4~800MHz,配合簡單的電阻網絡及濾波電容就可以完成設計任務了。

LTC2260的工作時鐘由FPGA提供,輸出1.8V的并行數據到FPGA進行處理,FPGA采用2.5V的I/O電壓。

FPGA和DSP的設計

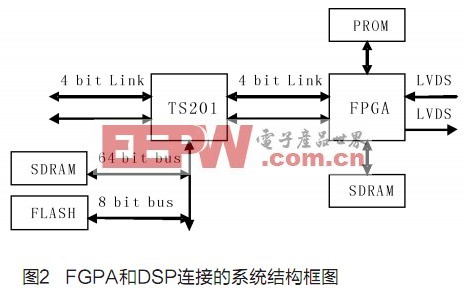

本系統采用松耦合結構設計,FPGA和DSP都有其各自獨立的存儲器,DSP和FPGA之間通過LINK進行互連,DSP與FPGA之間通信通過編寫FPGA仿TS201 LINK邏輯完成,DSP還可通過LINK與外部交換數據,系統結構框圖如圖2所示。這種連接方式的優點在于:

(1) DSP和FPGA片間數據交換數據率更高,最高可達4GB/s;

(2) DSP和FGPA可以同時訪問各自的外部存儲器,系統總的存儲帶寬較大;

(3) DSP和FPGA訪問外部存儲器的同時可以通過LINK鏈路進行數傳通信;

(4) 系統硬件連線相對獨立,易實現。

FPGA接口設計

FPGA主要提供3個邏輯接口,分別為與DSP的LINK接口、外部存儲器SDRAM的接口以及系統的輸入輸出接口。與DSP的LINK接口采用IP核設計實現,接口能夠穩定工作在500MHz速度上,為FPGA和DSP之間提供4GB/s的數據傳輸能力。

FPGA到SDRAM接口邏輯自行設計,與DSP外部存儲器相同采用4片K4S511632M 構成64bit的256MB存儲空間。接口工作在80MHz時鐘頻率,數據率為640MB/s。

FPGA的輸入輸出接口連接到系統外,因此采用LVDS協議來保證信號的穩定、準確傳輸,雙向各提供32bit數據寬度,采用250MHz的板間傳輸頻率,可以提供2GB/s的傳輸能力。

評論