TPACK與Cypress聯(lián)手為以太網(wǎng)交換和流量管理提供參考設(shè)計(jì)

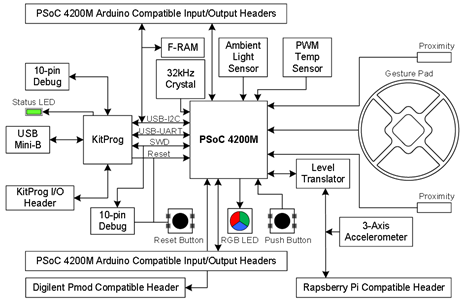

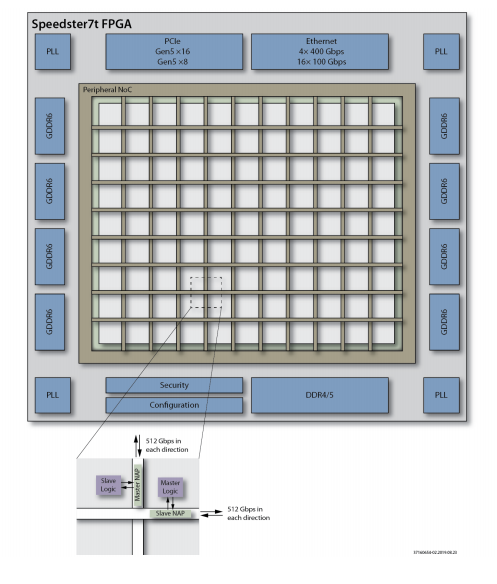

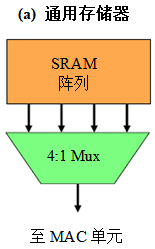

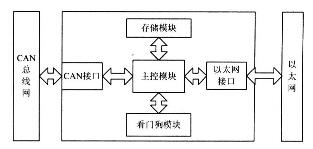

SRAM行業(yè)的領(lǐng)導(dǎo)者賽普拉斯,與領(lǐng)先的核心數(shù)據(jù)傳輸及交換功能IC的供應(yīng)商TPACK日前聯(lián)合宣布,為超高速以太網(wǎng)交換和排隊(duì)管理應(yīng)用推出一款參考設(shè)計(jì)。全新的Springbank參考設(shè)計(jì)結(jié)合了TPACK的 TPX4004高容量集成包處理器和流量管理器,以及賽普拉斯的CY7C15632KV18 72-Mbit Quad Data Rate™II+ (QDR™II+)SRAM,從而能提供最快的速度,并且未來升級(jí)非常簡單。TPACK參考設(shè)計(jì)還提供對(duì)各類FPGA的便捷接口,擁有強(qiáng)大的應(yīng)用支持。

本文引用地址:http://www.104case.com/article/107368.htmTPACK的高可靠性40-Gbps TPX4004提供真正的城域以太網(wǎng)論壇(MEF)定義的運(yùn)營商級(jí)別的性能。其超級(jí)靈活、功能豐富的第二層解決方案具有適應(yīng)不同系統(tǒng)架構(gòu)和要求的能力。賽普拉斯的QDRII+是業(yè)界首款量產(chǎn)的65-nm線寬SRAM。賽普拉斯的SRAM通過一個(gè)36-bit I/O的QDRII+器件,可以實(shí)現(xiàn)業(yè)界最快的高達(dá)550 MHz的時(shí)鐘速度以及80 Gbps的總數(shù)據(jù)率,而功耗只有90-nm SRAM的一半。

TPACK 產(chǎn)品線管理副總裁Thomas Rasmussen說:“能夠首先推出這款參考設(shè)計(jì),顯示了我們?cè)谟糜谶\(yùn)營商以太網(wǎng)交換和流量管理的高數(shù)據(jù)吞吐率外部存儲(chǔ)器解決方案領(lǐng)域的技術(shù)領(lǐng)導(dǎo)地位。與賽普拉斯這樣的SRAM領(lǐng)導(dǎo)者合作,保證了我們產(chǎn)品的最高性能和可靠性。”

賽普拉斯同步存儲(chǔ)器和時(shí)序產(chǎn)品副總裁David Kranzler說:“TPACK的高性能Springbank參考設(shè)計(jì)是個(gè)非常出色的平臺(tái),能夠充分展示我們65-nm QDRII+ SRAM在網(wǎng)絡(luò)市場的先進(jìn)設(shè)計(jì)中所具有的驚人速度。我們期待在未來的項(xiàng)目上與TPACK就SRAM和我們強(qiáng)大的用于網(wǎng)絡(luò)的時(shí)序解決方案產(chǎn)品線繼續(xù)合作。”

與其90-nm前輩相比,賽普拉斯的65-nm QDR 和 DDR SRAM將輸入和輸出電容減少了60%。QDRII+ 和 DDRII+器件具有片內(nèi)終結(jié)器(ODT),因?yàn)椴恍枰獠恐袛嚯娮瑁阅芨纳菩盘?hào)的完整性,降低系統(tǒng)成本并節(jié)約板級(jí)空間。65-nm器件采用了先進(jìn)設(shè)計(jì)和技術(shù),使得數(shù)據(jù)有效窗口拓寬了35%,從而為客戶節(jié)省了研發(fā)時(shí)間和成本。

評(píng)論