Open Drain上下拉電阻計算

集成芯片的數字輸出引腳分為開漏(OD, Open Drain)和推挽(Push-Pull)結構。開漏結構可以進行并聯實現或邏輯,在后級芯片識別邏輯與本身耐壓范圍內可以拉到系統的任何電壓,使用十分靈活。芯片上常見的OD結構輸出常見于DCDC芯片的PG(Power Good)和 LBO (Low Battery),電壓監控復位芯片的Reset 和 PFO(Power Fail)等,所有漏開輸出都需要使用外部上拉或下拉電阻來保持數字輸出處于定義的邏輯狀態。

處理OD 輸出時,首先需要考慮是需要上拉電阻還是下拉電阻,然后考慮電阻的阻值。

一、計算上拉電阻范圍

芯片發出動作信號驅動低輸出時則需要上拉電阻。例如TPS62085,具有PG輸出,如果芯片的輸出電壓不處于調節狀態,它將驅動低電平。因此,PG需要一個上拉電阻,當芯片允許PG引腳浮動時,它將PG引腳拉高,表明電源良好,使能下級芯片,保證系統正常運行。

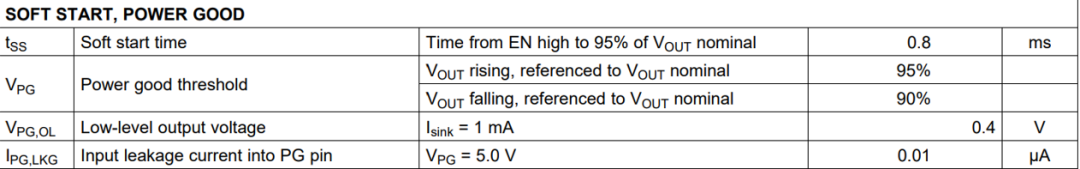

*附 TPS62085數據手冊PG相關數據。

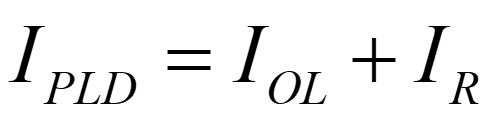

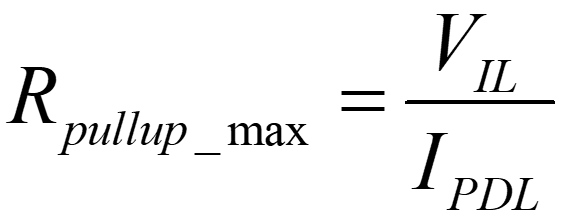

1.當電源良好,Q1處于關閉狀態時,設計 Rpull-up 最大值:

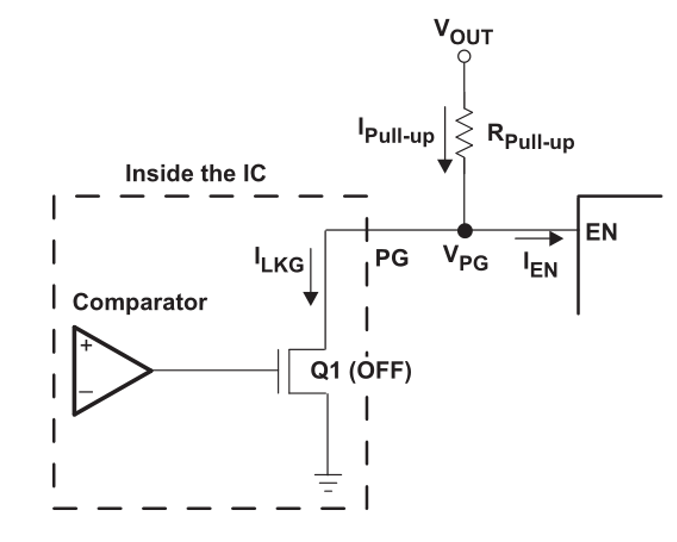

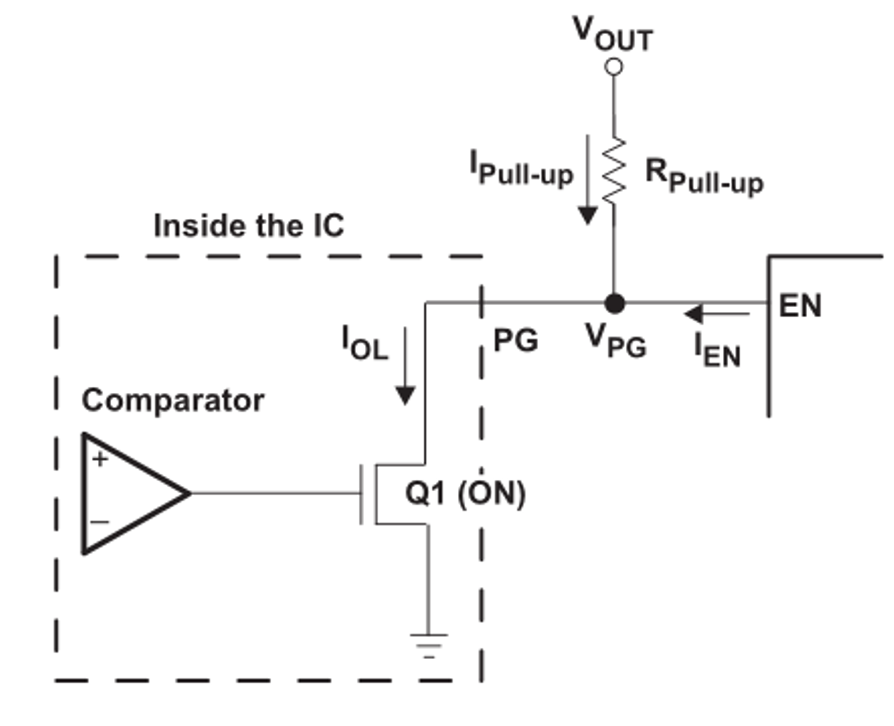

典型PG輸出電路(PG浮高)

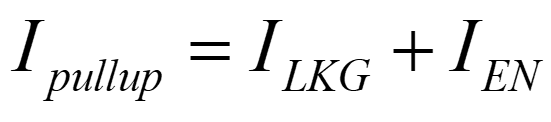

當Q1關閉,ILKG與IEN 在上拉電阻上產生壓降,因此到EN上電壓會有降低,為了滿足下級芯片EN邏輯高電平。

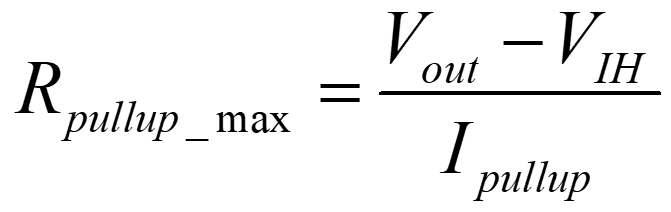

如果選擇更大的電阻會導致RPull-up上的電壓降更大,這將導致VPG低于VIH的最小值。后級芯片無法識別PG電壓為邏輯高。

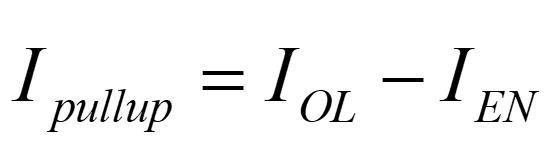

2.同樣的,當Q1打開,設計 Rpull-up 最小值:

典型PG輸出電路(PG低電平)

Q1開通 導通電阻Rdson使得PG電壓高于0V。當Q1接通時,PG電壓必須足夠低,以shutdown后級芯片。IOL在數據手冊作為PG輸出低電平 VOL的測試電流。VOL在IOL下不會超過其規定的最大電壓。可以使用達到指定的絕對最大PG吸收電流的電流,但它們可能產生高于其指定最大值的VOL。IC的測試電流和后級EN輸入的漏電流相減為流過上拉電阻的電流。

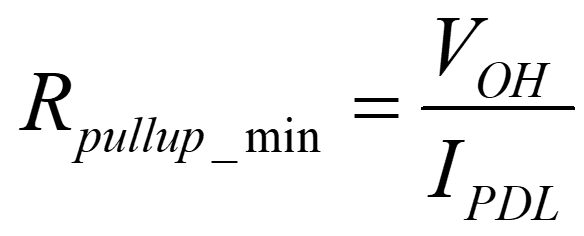

上拉電阻兩端的電壓等于Vout減去VPG。VPG此時的最大值VOL=0.4 V。電阻的最小值需要保證Q1中流過電流小于IOL。大于IOL會導致Q1壓降無法保證低于0.4V。為了確保符合測試條件,保證VOL最大不超過0.4V,可通過下式計算出最小上拉阻力。

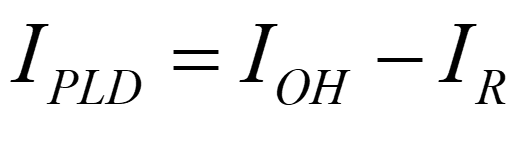

二、計算下拉電阻范圍

同理去分析即可得到電阻范圍。

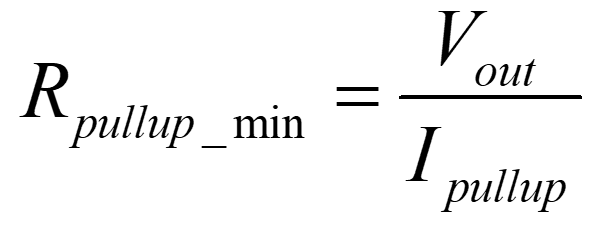

1.當輸出不動作,Q1處于關閉狀態時,設計 Rpull-down 最大值:

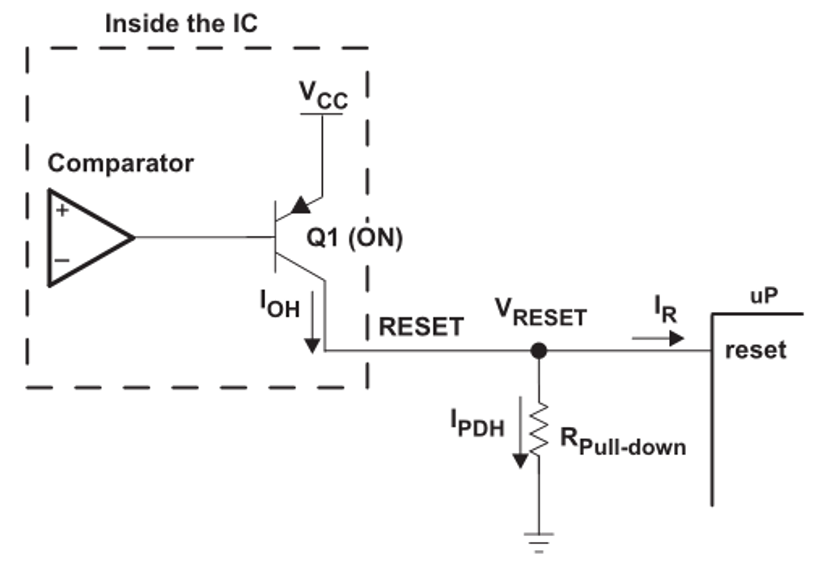

Reset輸出等效電路(Reset浮低)

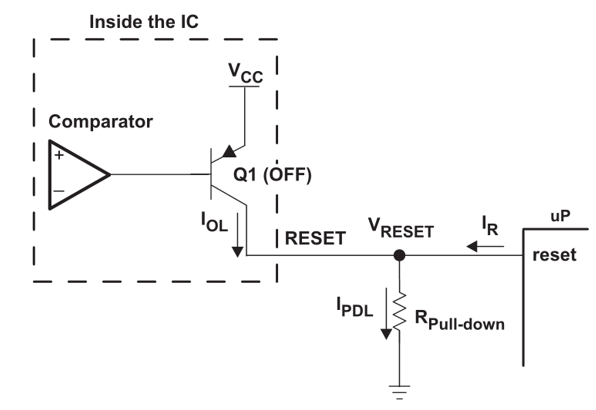

2.當Q1打開,設計Rpull-down 最小值:

Reset輸出等效電路(Reset高電平)

實際數據手冊會給出建議上拉/下拉的電阻阻值,而且一般電阻可選范圍較寬(1k~500kΩ),使用建議值是最方便可以保證系統正常工作。

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。