D類功放“爆破音”機理與抑制措施淺析

D類功率放大器以高輸出功率,高效率,小體積等優點,在車載音響領域異軍突起。在數字D類功放剛上電或功放播放狀態切換時,人耳偶爾會聽到“嘣”的聲音,我們把這個爆破的聲音稱為pop noise。數字功放pop noise 出現的原因有很多,本文主要分析pop noise出現原因,并提供相應解決方法。

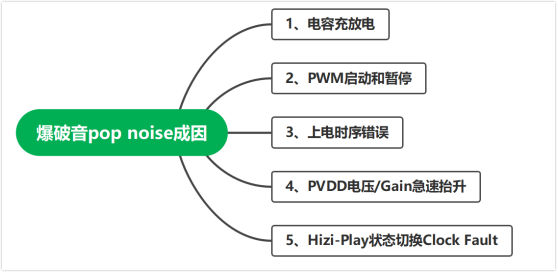

Pop noise成因有以下5點:

下面關于5點原因都做一個簡單介紹。

1、電容充放電

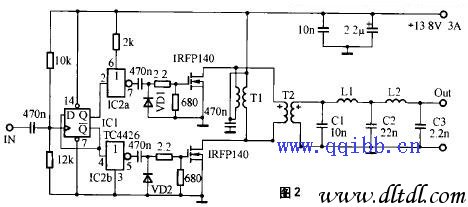

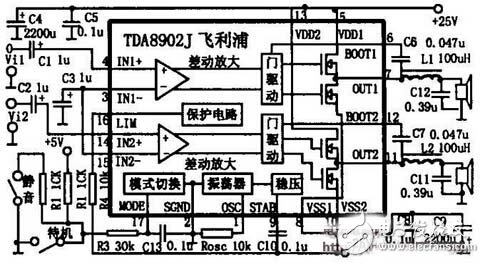

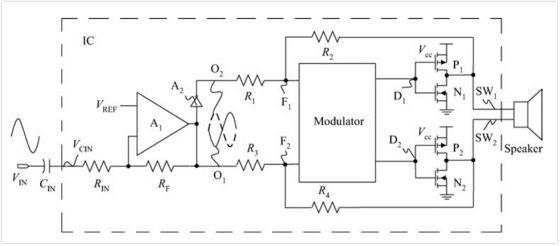

上圖所示為單端輸入功放,A1是比較放大器,用于設置增益,增強輸入信號的負載能力。A2輸出同A1輸出完全反向。Modulator用于信號調制,將輸入的模擬信號與三角波比較,生成PWM波驅動外圍MOS。比較放大器A1的一端直連參考電壓Vref,另一端通過RIN、CIN連接輸入音頻信號。

在系統上電時,Vref立刻上升到參考電壓值,而A1的另一端則需要通過給RIN、CIN充電,在經一段時間后才能上升到參考電壓值。A1兩端的電壓差經放大后,輸出產生pop noise。該場景下可通過降低輸入電容值,如換成1uf或0.47uf來實現降低 pop noise。

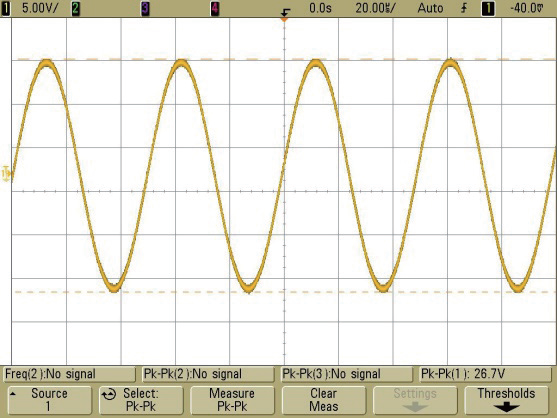

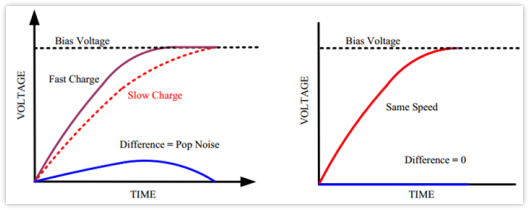

對于差分功放而言,如果P端和N端的輸出外圍硬件電路不匹配或者輸入外圍硬件電路不匹配,功放兩端輸入信號建立時間會不一樣,該差分信號差也會輸入功放并形成pop音。如下圖所示,若A1兩端電壓上升速度一致,pop noise為0。5ns的信號建立時間差即可產生人耳可聽到的pop音。

不同充電速度下的POP Noise

2、PWM啟動和暫停

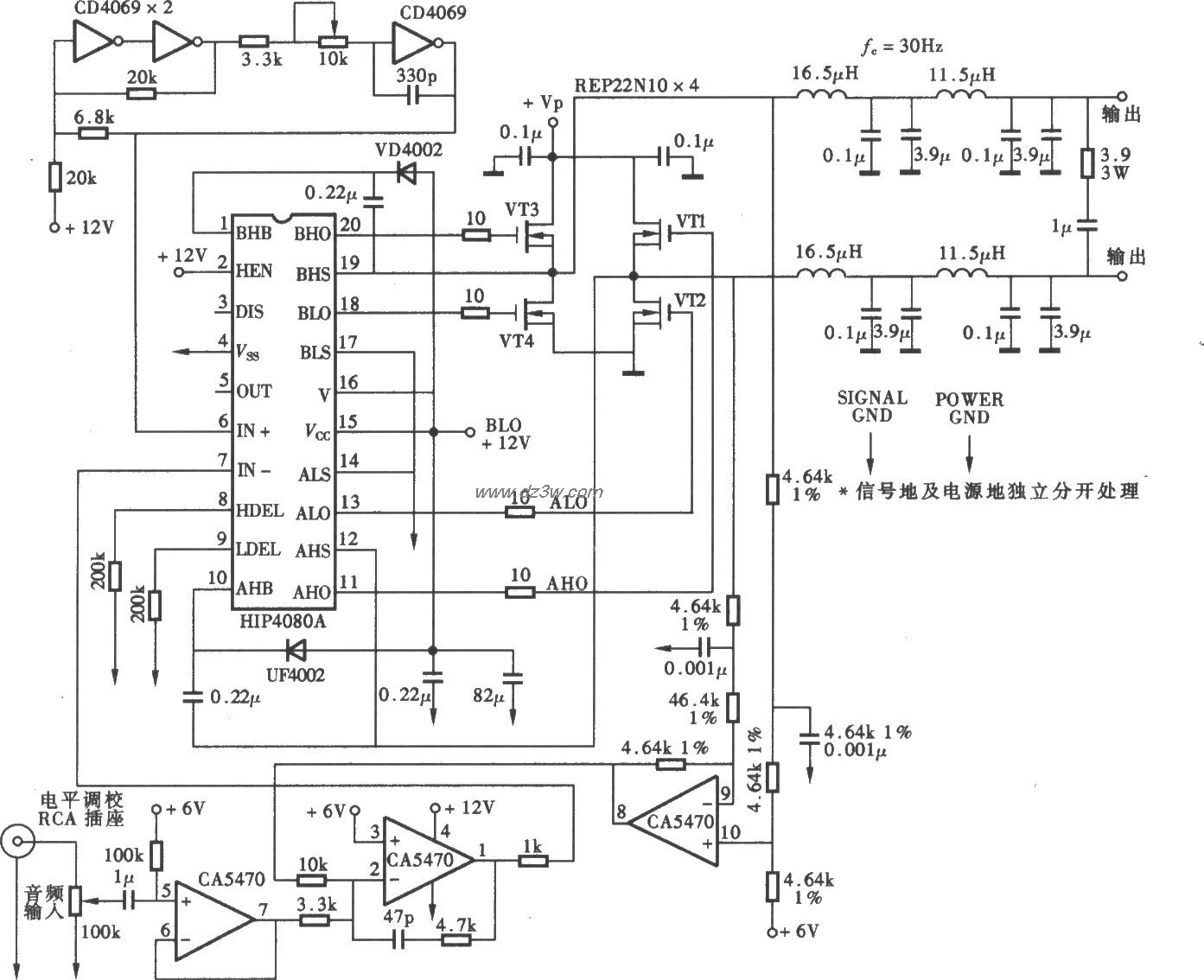

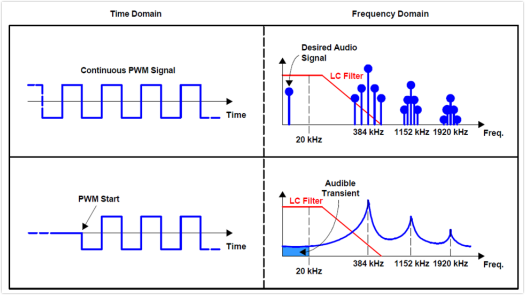

在系統掉電或上電,功放播放狀態切換,或輸入音源切換時,PWM會產生啟停,進而產生瞬態的POP音。如下圖所示,在連續PWM動作時,開關頻率及其附近的鏡像頻率都可以順利的被LC濾波器濾除。而在PWM啟停時,開關頻率及其奇次諧波會延伸到人耳可聽的20-2kHz范圍內。該開關頻率低于LC濾波器的截止頻率,不能被濾除進而產生pop音。

連續PWM及PWM啟動的時頻域圖:

對于BTL結構的功放在進行AD調制時,PWM開啟第一個Duty cycle,如果A-side拉低,Bootstrap 電容可以順利充電,但B-side在此時拉高,這使得Bootstrap電容充電失敗。Bootstrap電容提供N MOSFET的充電電壓,如Bootstrap電容充電失敗,則B-side 第一個PWM不能正常輸出。A-side和B-side的不平衡輸出會產生明顯的POP音。TI針對該類pop noise進行了優化,在AD和BD調制中,都使得第一個PWM為低,進而消除Clock fault。

AD調制PWM開啟示意圖

3、上下電順序錯誤

音頻系統有嚴格的上下電順序。通常功放的供電電壓會比SOC的供電電壓高,也比SOC電壓建立時間早。為避免pop noise在SOC上電及功放上電時發生,要保持功放為Hi-zi/standby狀態,且待功放充分充電后(20ms),再開啟PWM波,輸入音源。同理在功放斷電時,為避免掉電速度不一致,我們需要Mute 并將Standby引腳拉低15ms后再進行掉電。TI 的PurePath Digital 具有優化后的啟動序列,這使得可聽音頻帶的pop音盡可能小。

4、PVDD電壓/Gain值急速抬升

PVDD電壓急劇上升或Gain值急速抬升均會導致pop noise 出現。在進行原理圖繪制時,需要將Cstart軟啟動電容設置在合理的范圍內,防止PVDD急速上升。此外,針對某些功放在開機第一次POP noise出現后,還出現了第二次pop noise。這是因為功放在上電后,增益值會以一定步長爬升到設定增益,如果步長設定值過大,會導致pop noise的出現。

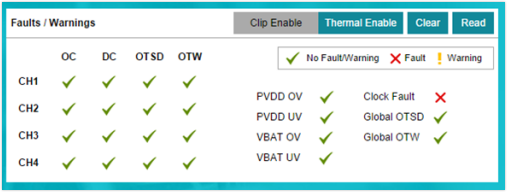

5、Hizi-play 狀態切換Clock Fault

如果喇叭不僅僅在開機或者狀態轉換時出現pop 音,而是當功放從Hi-zi切換到play時,連續出現POP noise,此時應當檢查是否出現Clock Fault。以TI的芯片TAS6424L/M-Q1系列為例,硬件工程師可以斷開SOC的IIC控制,并將IIC通過USB轉接板連接到PPC3進行Clock Fault檢驗。

若此時出現Clock Fault 應檢查輸入音頻信號I2S/TDM是否滿足數據手冊的要求(見數據手冊Electrical Characteristics 中Serial Audio Port)。此外,數據手冊中還有其他特殊情況的說明,以TAS6424L/M-Q1系列為例,如果客戶將SCLK和MCLK連接到一起,FSYNC需要為2 MCLK以上。若SOC為高通8155系列,FYSNC輸出共有3個選項:第一是2MCLK ,第二是50% duty cycle ,第三為1 slot,我們可以選擇后兩項作為FSYNC輸入。

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。