美光:下一代DRAM技術面臨哪些困境?

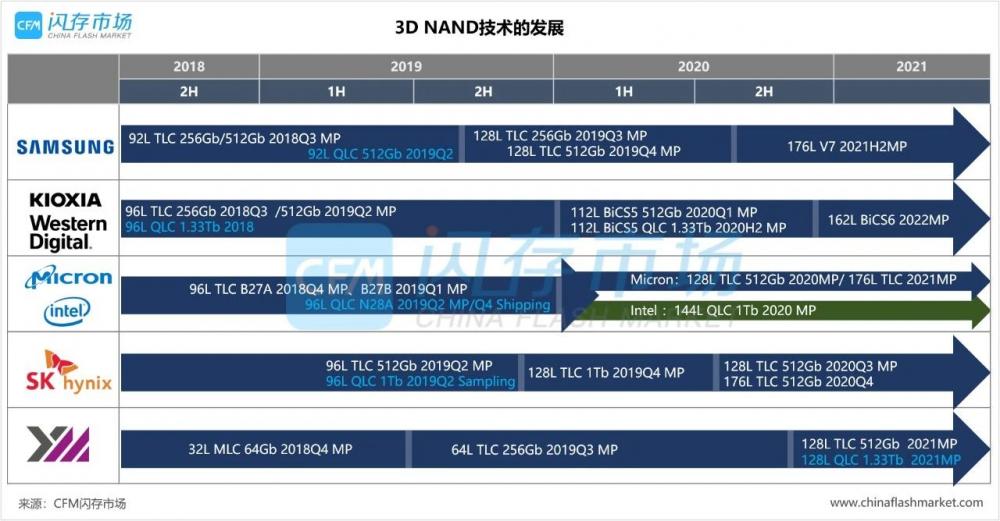

近年來,在原廠之間的技術角逐之中,美光可謂成績亮眼,無論在DRAM還是NAND領域都可謂“一馬當先”,不僅率先批量生產176層3D NAND Flash,也是第一個宣布批量出貨1α DRAM產品的廠商。

另外,在DRAM領域,美光更是三家內存原廠中唯一在1α制程中沒有導入EUV工藝的廠商。近日有報道稱,美光最新1α制程產品擁有0.315Gb/mm2的存儲密度,half pitch為14.3nm,超越了三星1z制程工藝0.299 Gb/mm2的存儲密度,是當前業內存儲密度最高的產品。

那么,美光作為DRAM技術發展的有力推手,在下一代DRAM技術中面臨哪些技術和性能挑戰?無疑對產業鏈具有借鑒作用。在一次技術交流會上,美光對此做了詳細闡述,并以《Scaling and Performance Challenges of Future DRAM》為題公開發表。

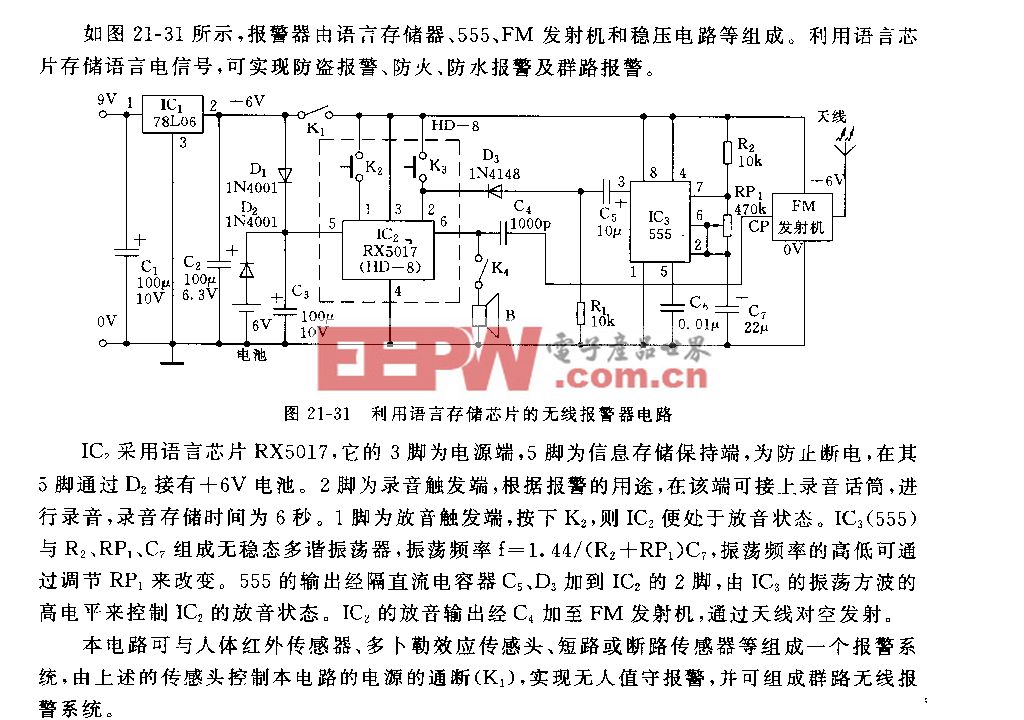

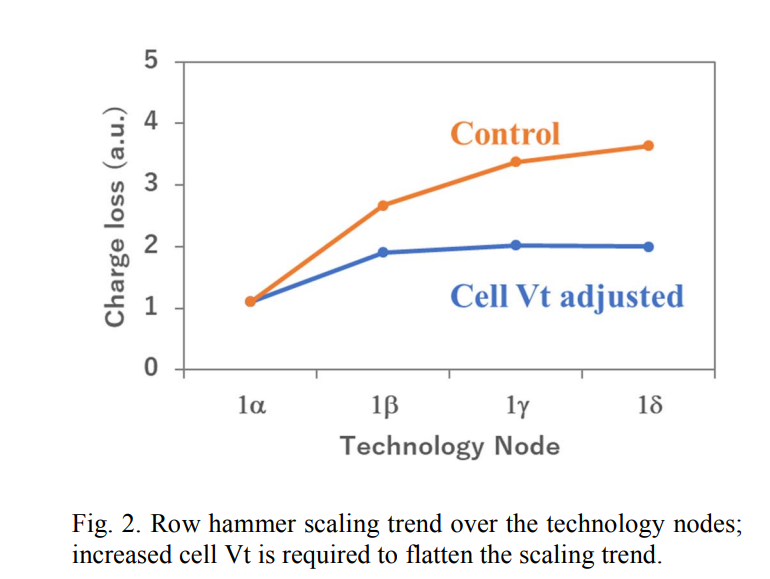

Row Hammer攻擊

所謂Row Hammer攻擊是指為了內存容量的增加,DRAM cell越做越小且距離越來越近,導致存儲器單元泄露電荷并可能造成比特翻轉的意外情況。

圖片來源:Scaling and Performance Challenges of Future DRAM

Row Hammer問題并非新增問題,并將在DRAM微縮過程中愈發嚴重。雖然,當前通過采用ECC糾錯技術緩解了這種情況,卻仍然存在一定的限制。而在1β制程技術中,若要緩解Row Hammer問題,則需要突破性技術改善。

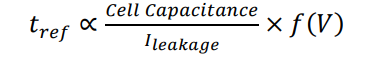

刷新周期

所謂刷新周期是指對所有DRAM存儲單元恢復一次原狀態所需的時間間隔。由于DRAM的存儲位元是基于電容器的電荷存儲,這個電荷量會隨著時間和溫度而減少,因此必須定期的刷新,以保持它們原來記憶的正確信息。

根據公式,刷新周期與單位電容成正比,隨著DRAM技術尺寸微縮,刷新周期性能也將下降。另外,在一定刷新周期內,錯誤率也將隨著溫度的升高而增加。而這一特性限制了產品在汽車領域的使用,因為在汽車領域中,通常對器件的溫寬要求很高。

來源:Scaling and Performance Challenges of Future DRAM

感測容限和Vt補償感測放大器(Sensing margin & VT compensated sense amplifier)

隨著DRAM器件尺寸微縮,感測容限不斷降低,且由于每個節點的窄通道效應和短通道效應,感測放大器晶體管Vt的變化加劇。

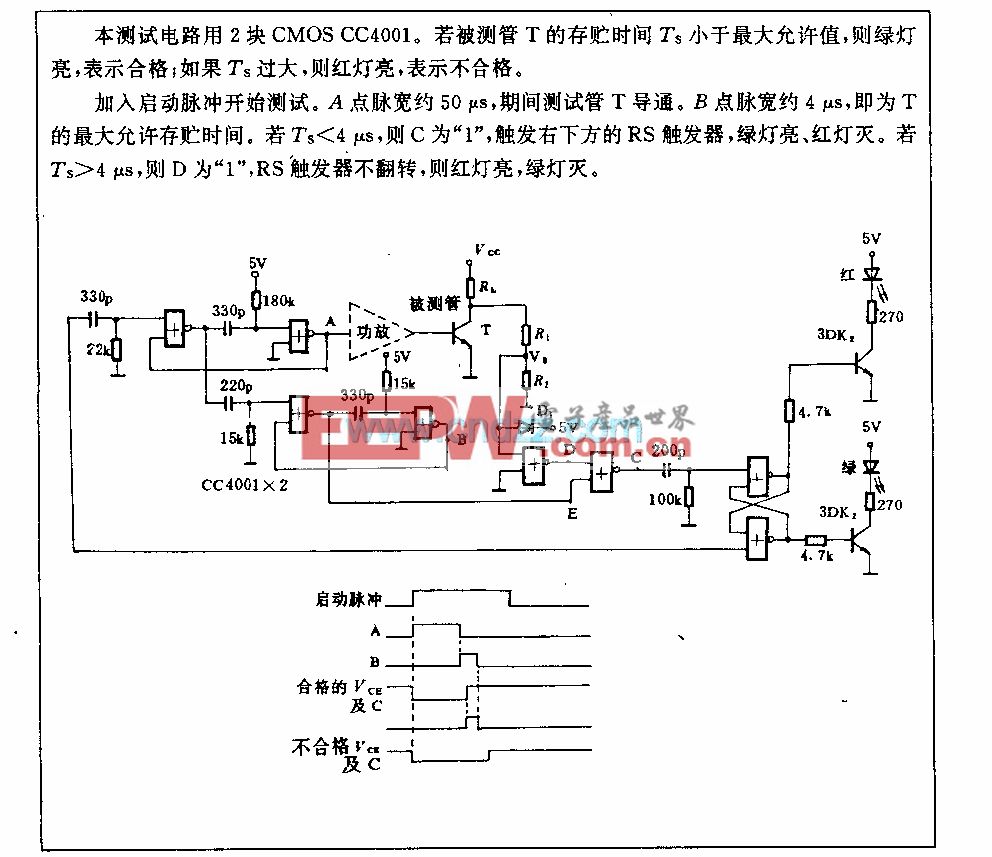

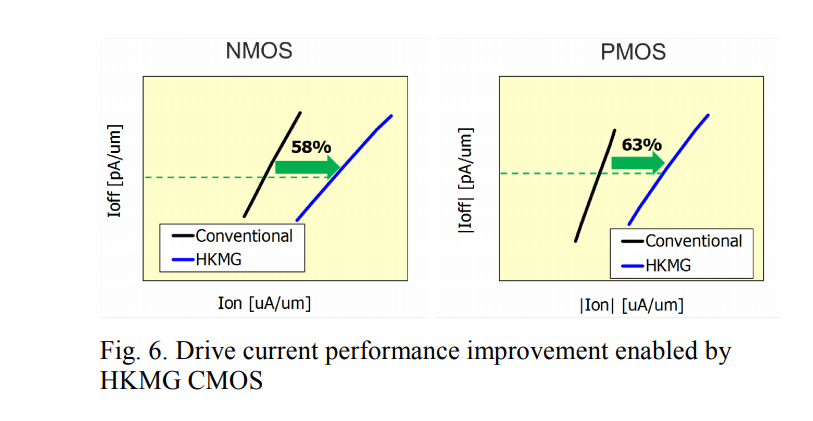

CMOS技術

隨著CMOS電路不斷縮小,晶體管的關鍵指標:柵氧厚度不斷縮小,然而當厚度縮小到2nm以下時,就會出現明顯的隧穿泄露。因此邏輯芯片廠商開始使用High-K工藝,就是使用高介電常數的物質替代二氧化硅。

近十年中,DRAM芯片中也使用了High-K工藝,使得DRAM性能提升的同時降低功耗。在DRAM歷史上,隨著數據速率提高以及功耗要求提升,DRAM工作電壓已經從5V降低到1.05V。隨著DRAM性能要求的分化,CMOS性能有望縮小與邏輯CMOS之間的差距。

圖片來源:Scaling and Performance Challenges of Future DRAM

隨著數據量增加以及對器件性能要求的提升,在實現1α以下DRAM技術的發展過程中將面臨許多挑戰。存儲廠商將不斷開創創新的工藝與材料開發來克服這些挑戰,持續提供突破和創新的設計方法,滿足未來的性能及規模需求。

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。