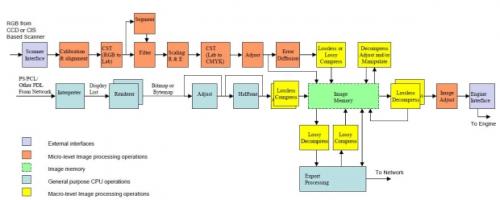

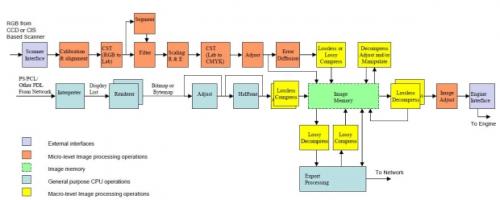

- 在高性能計算、娛樂和科學計算市場,OpenCL的采用在持續增長。OpenCL的靈活性和便攜性使之成為了一個開發圖像處理應用的優秀平臺。然而,OpenCL尚未應用到硬拷貝打印機和多功能打印機(MFP)市場。傳統上,打印機/MFP市場使用全定制系統級芯片(SoC或ASIC)、專用集成電路進行圖像處理。在本文中,我們探討了配合Altera SoC FPGA(現場可編程門陣列)的OpenCL在核心MFP圖像處理流水線中的應用。核心圖像處理流水線以每分鐘大于90頁信紙大小的全色RGB持續速率運行,圖像分辨率為6

- 關鍵字:

FPGA OpenCL

- 2014年9月至2015年1月期間,6,000多名來自全球各地的工程師(其中4,000名來自亞洲)參加了安富利在全球37個城市舉辦的X-fest 系列技術研討會,聽取了有關采用 Xilinx® 7系列、Zynq®-7000 All Programmable SoC 和 UltraScale™系列器件進行設計的專家指導。

安富利公司 (Avnet, Inc.) 旗下營運機構安富利電子元件亞洲 (Avnet Electronics Marketing Asia) 今天起還

- 關鍵字:

Xilinx UltraScale

- 一、 引言

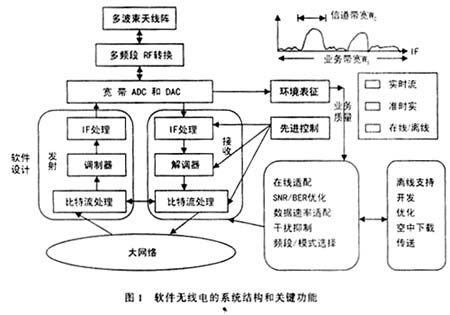

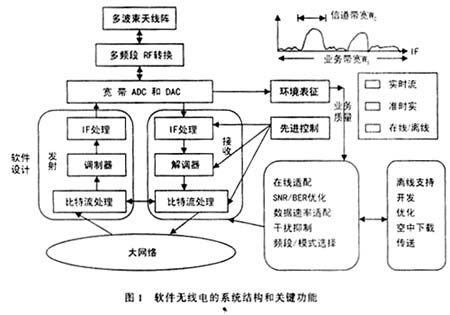

現代通信技術、微電子技術和計算機技術的飛速發展,促進了無線通信技術從數字化走向軟件化。軟件無線電的出現掀起了無線通信技術的又一次革命,它已經成為目前通信領域中最為重要的研究方向之一。所謂軟件無線電,是指構造一個通用的、可重復編程的硬件平臺,使其工作頻段、調制解調方式、業務種類、數據速率與格式、控制協議等都可以進行重構和控制,選用不同的軟件模塊就可以實現不同類型和功能的無線電臺,其核心思想是在盡可能靠近天線的地方使用寬帶A/D和D/A變換器,并盡可能地用軟件來定義無線功能[1]。

- 關鍵字:

FPGA 無線電

- 軟件無線電的出現,是無線電通信從模擬到數字、從固定到移動后,由硬件到軟件的第三次變革。簡單地說,軟件無線電就是一種基于通用硬件平臺,并通 過軟件可提供多種服務的、適應多種標準的、多頻帶多模式的、可重構可編程的無線電系統。軟件無線電的關鍵思想是,將AD(DA)盡可能靠近天線和用軟件來 完成盡可能多的無線電功能。

蜂窩移動通信系統已經發展到第三代,3G系統進入商業運行一方面需要解決不同標準的系統間的兼容性;另一方 面要求系統具有高度的靈活性和擴展升級能力,軟件無線電技術無疑是最好的解決方案。用ASI

- 關鍵字:

無線電 FPGA

- 心率監控器是一款用于監測人體心跳速率的器件。心率的單位是bpm(每分鐘心跳數)。人體的心跳速率根據其日常身體活動、睡眠和基本健康狀況的不同而有所差別。本文為大家介紹幾種心率計及心率監測系統的設計,供大家使用參考。

基于EFM32TG840的便攜式心率計的設計方案

在消費電子領域,便攜式電子產品由于體積小、質量輕的特點越來越受到消費者的喜愛,已成為人們生活中不可缺少的部分。基于這個思路,我們設計了一款便攜式心率計,它可以替代用脈搏聽診器等進行測量的傳統方法,使用非常方便。

一種便攜式單

- 關鍵字:

FPGA VHDL

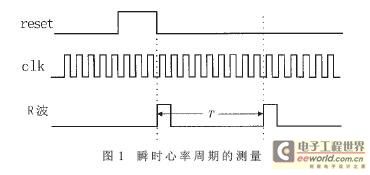

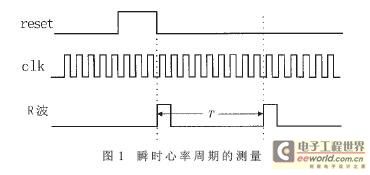

- 心率計是常用的醫學檢查設備,實時準確的心率測量在病人監控、臨床治療及體育競賽等方面都有著廣泛的應用。心率測量包括瞬時心率測量和平均心率測量。瞬時心率不僅能夠反映心率的快慢。同時能反映心率是否勻齊;平均心率雖只能反映心率的快慢,但記錄方便,因此這兩個參數在測量時都是必要的。

測量心率有模擬和數字兩種方法。模擬方法是在給定的時間間隔內計算R波(或脈搏波)的脈沖個數,然后將脈沖計數乘以一個適當的常數測量心率的。這種方法的缺點是測量誤差較大、元件參數調試困難、可靠性差。數字方法是先測量相鄰R波之間的時間

- 關鍵字:

FPGA 心率計

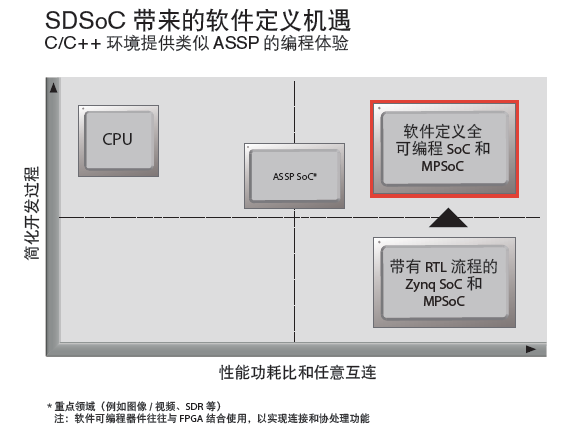

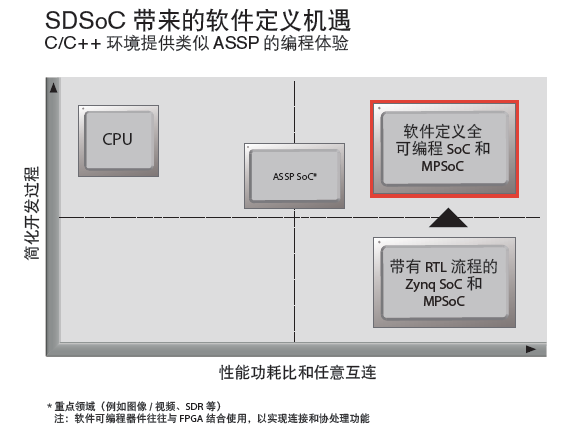

- 最近,Xilinx發布了面向其嵌入式處理器Zynq的SDSoC開發環境(http://www.104case.com/article/270768.htm),目的是使不懂硬件的系統架構師和軟件架構師也能直接使用Zynq,在Zynq上用C/C++編程。而過去,只能通過HDL(高層次語言)的RTL(寄存器傳輸級)語言來編程,一般的軟件工程師很難掌握。

為了展示SDSoC的強大性,Zynq業務發展經理羅霖(下圖)向大家演示了軟件開發便捷性,只見不到十分鐘,羅霖就編好了一款視頻程序,并沖著攝像頭揮手

- 關鍵字:

Xilinx SDSoC

- 七、 測試平臺設計

本實驗主要對LED的輸出和輸入與復位的關系進行測試仿真,通過仿真,即可驗證設計的正確性和合理性。相關testbench的代碼如下:

以下是代碼片段:

`timescale 1ns/1ns

module LED_Driver_tb;

reg Rst_n;

reg [3:0] Sig;

wire [3:0] Led;

LED_Driver

#( /*參數例化*/

.Width (4)

)

LED_Driver_in

- 關鍵字:

FPGA LED

- 在之前更新的目錄里面,并沒有安排這個實驗,第一個實驗應該是獨立按鍵的檢測與消抖。可是,當小梅哥來做按鍵消抖的實驗時,才發現沒有做基本的輸出設備,因此按鍵檢測的結果無法直觀的展示出來。也算是為后續實驗做鋪墊吧,第一個實驗就安排成了點亮LED燈。

一、 實驗目的

實現4個LED燈的亮滅控制

二、 實驗原理

LED燈的典型電路如下2-1所示,我們控制led燈的亮滅,實質就是去控制FPGA的IO輸給LED負極一個低電平或者高電平。從圖中可知,我們給對應的led負極上一個低電平,就會有對

- 關鍵字:

FPGA LED

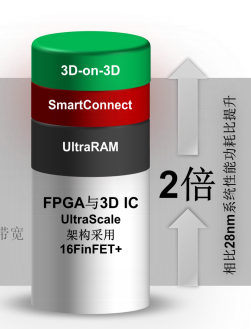

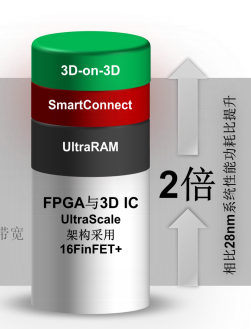

- 2月底,Xilinx發布了下一代16nm產品特點的新聞:《Xilinx憑借新型存儲器、3D-on-3D 和多處理SoC技術在16nm繼續遙遙領先》(http://www.104case.com/article/270122.htm),大意是說,Xilinx新的16nm FPGA和SoC中,將會采用新型存儲器UltraRAM, 3D晶體管(FinFET)和3D封裝,Zynq會出多處理器產品MPSoC,因此繼28nm和20nm之后,繼續在行業中保持領先,打破了業內這樣的規則:Xilinx和競爭對手在工藝上

- 關鍵字:

Xilinx FPGA

- 電能質量即電力系統中電能的質量。理想的電能應該是完美對稱的正弦波。一些因素會使波形偏離對稱正弦,由此便產生了電能質量問題。一方面我們研究存在哪些影響因素會導致電能質量問題,一方面我們研究這些因素會導致哪些方面的問題,最后,我們要研究如何消除這些因素,從而最大程度上使電能接近正弦波。本文為您介紹電能質量的檢測與分析儀器設計匯總。

基于STM32和ATT7022C的電能質量監測終端的設計

本文以ARM STM32F103VE6和電表芯片ATT7022C為主構建了電能質量監測終端,利用電表芯片A

- 關鍵字:

ARM FPGA NiosⅡ

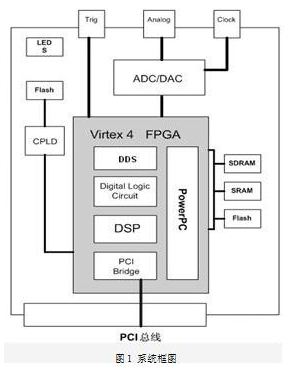

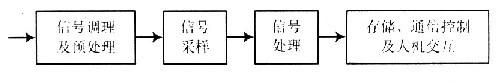

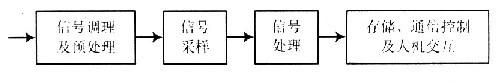

- 在電力系統中,要實現對電能質量各項參數的實時監測和記錄,必須對電能進行高速的采集和處理,尤其是針對電能質量的各次諧波的分析和運算,系統要完成大量運算處理工作,同時系統還要實現和外部系統的通信、控制、人機接口等功能。而電能質量監測系統大多以微控制器或(與)DSP為核心的軟硬件平臺結構以及相應的設計開發模式,存在著處理能力不足、可靠性差、更新換代困難等弊端。本文將SoPC技術應用到電力領域,在FPGA中嵌入了32位NiosⅡ軟核系統。可實現對電能信號的采集、處理、存儲與顯示等功能,實現了實時系統的要求。

- 關鍵字:

FPGA NiosⅡ

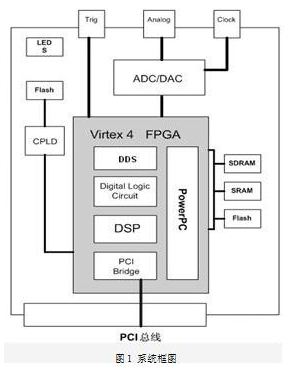

- 隨著可編程邏輯器件的不斷進步和發展,FPGA在嵌入式系統中發揮著越來越重要的作用。本文介紹的在電能質量監測系統中信號采集模塊控制器的 IP核,是采用硬件描述語言來實現的。首先它是以ADS8364芯片為控制對象,結合實際電路,將6通道同步采樣的16位數據存儲到FIFO控制器。當FIFO 控制器存儲一個周期的數據后,產生一個中斷信號,由PowerPC對其進行高速讀取。這樣能夠減輕CPU的負擔,不需要頻繁地對6通道的采樣數據進行讀取,節省了CPU運算資源。

1 ADS8364芯片的原理與具體應用

- 關鍵字:

FPGA 信號采集

- 賽靈思公司 (Xilinx+)日前宣布,其16nm UltraScale+? 系列FPGA、3D IC和MPSoC憑借新型存儲器、3D-on-3D和多處理SoC(MPSoC)技術,再次實現了領先的價值優勢。此外,為實現更高的性能和集成度,UltraScale+系列還采用了全新的互聯優化技術——SmartConnect。這些新的器件進一步擴展了賽靈思的UltraScale產品系列 (現從20nm 跨越至 16nm FPGA、SoC 和3D IC器件),同時利用臺積電公

- 關鍵字:

賽靈思 FPGA SoC UltraScale 201503

- ?????? 京微雅格(北京)科技有限公司(以下簡稱“京微雅格”)宣布將參加 3月 17 日至 19 日在上海舉行的 2015慕尼黑上海電子展。活動期間,京微雅格將展示其FPGA產品在多個市場領域的應用方案,包括消費電子、智能家居、金融安全、機器人、物聯網、汽車電子等。京微雅格展位號為半導體E3館3646,誠邀您蒞臨參觀。

?

圖一:將在慕尼黑上海電子展期間現場展示的部分已量產芯片

FP

- 關鍵字:

京微雅格 FPGA

xilinx fpga介紹

Xilinx FPGA

Xilinx FPGA主要分為兩大類,一種側重低成本應用,容量中等,性能可以滿足一般的邏輯設計要求,如Spartan系列;還有一種側重于高性能應用,容量大,性能能滿足各類高端應用,如Virtex系列,用戶可以根據自己實際應用要求進行選擇。 在性能可以滿足的情況下,優先選擇低成本器件。

Xilinx FPGA可編程邏輯解決方案縮短了電子設備制造商開發產品的時間 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473