- 一、多路彩燈控制器設計原理設計一個彩燈控制程序器。可以實現四種花型循環變化,有復位開關。整個系統共有三個輸入信號CLK,RST,SelMode,八個輸出信號控制八個彩燈。時鐘信號CLK脈沖由系統的晶振產生。各種不同花

- 關鍵字:

VHDL 多路 燈控 制器設計

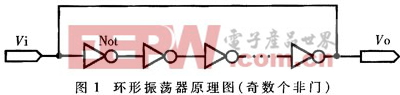

- 采用CPLD的片內環形振蕩器的方案設計,本文介紹一種通用的基于CPLD的片內振蕩器設計方法,它基于環形振蕩器原理,只占用片上普通邏輯資源(LE),無需使用專用邏輯資源(如MaxII中的UFM),從而提高了芯片的資源利用率;振蕩頻率可在一定范圍內調整,振蕩輸出

- 關鍵字:

方案設計 振蕩器 內環 CPLD 采用

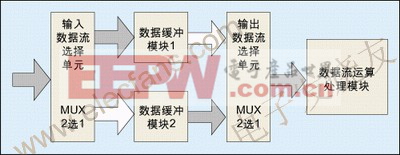

- FPGA/CPLD設計思想與技巧簡介,本文討論的四種常用FPGA/CPLD設計思想與技巧:乒乓操作、串并轉換、流水線操作、數據接口同步化,都是FPGA/CPLD邏輯設計的內在規律的體現,合理地采用這些設計思想能在FPGA/CPLD設計工作中取得事半功倍的效果。 F

- 關鍵字:

簡介 技巧 設計思想 FPGA/CPLD

- 隨著科技的飛速發展、高分辨率的數模混合電路的應用不斷深入,電路設計日趨復雜,精度越來越高,所以高精度AD轉換電路的設計就成了儀器儀表及各種測量控制系統的難點。本系統來源于儀器儀表的溫控系統設計,采用高精

- 關鍵字:

CPLD VFC AD轉換器

- 1 引 言EDA是現代電子系統設計的關鍵技術。硬件描述語言VHDL以其“代碼復用”(code re-use)遠高于傳統的原理圖輸入法等諸多優點,逐漸成為EDA技術中主要的輸入工具。然而,基于IEEE VHDL Std 1076-1993標準

- 關鍵字:

VHDL-AMS 控制系統 分析 中的應用

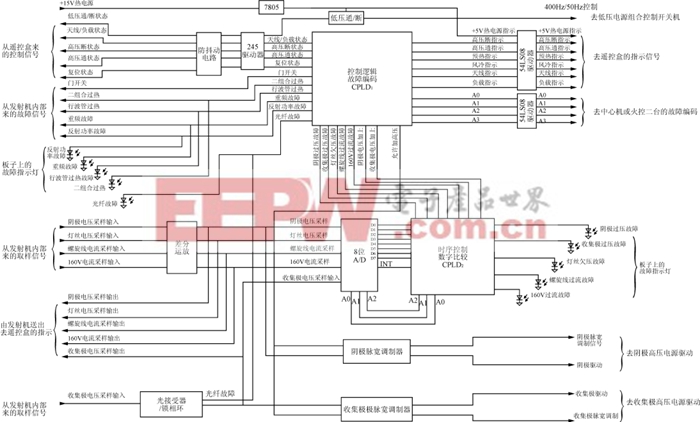

- 摘要:可編程控制器(PLD)自20世紀60年代末出現以來,就以其靈活、高效、可靠性高等優點受到設計者的青睞。而CPLD是20世紀90年代推出的一種復雜的PLD,其主要特征是集成規模大于1000門以上的可編程邏輯器件。它以其

- 關鍵字:

系統 介紹 保護 控制 CPLD 發射機 基于

- 1 引言隨著社會的發展。使用電梯越來越普遍,已從原來只在商業大廈、賓館過渡到在辦公室、居民樓等多種建筑中,并且對電梯功能的要求也不斷提高,其相應控制方式也在不斷發生變化。電梯的微機化控制主要有:PLC控制、

- 關鍵字:

CPLD VDHL 器件 電梯控制系統

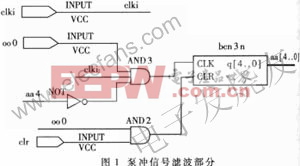

- 基于CPLD的數字濾波及抗干擾實現,1 濾波和抗干擾概述

單片機應用系統的輸入信號常含有種種噪聲和干擾,它們來自被測信號源、傳感器、外界干擾源等。為了提高測量和控制精度,必須消除信號中的噪聲和干擾。噪聲有兩大類:一類為周期性的;另一類為

- 關鍵字:

抗干擾 實現 波及 數字 CPLD 基于

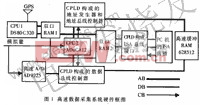

- 基于CPLD和MAX7000系列的數據采集系統簡介,CPLD是復雜的PLD,專指那些集成規模大于1000門以上的可編程邏輯器件。它由與陣列、或陣列、輸入緩沖電路、輸出宏單元組成,具有門電路集成度高、可配置為多種輸入輸出形式、多時鐘驅動、內含ROM或FLASH(部分支持在系

- 關鍵字:

系統 簡介 數據采集 系列 CPLD MAX7000 基于

- 電子產品世界,為電子工程師提供全面的電子產品信息和行業解決方案,是電子工程師的技術中心和交流中心,是電子產品的市場中心,EEPW 20年的品牌歷史,是電子工程師的網絡家園

- 關鍵字:

DSP FPGA CPLD

- 摘 要:本控制儀以單片機80c196kc為核心,集無功補償、電度量計量、電能質量監測及通信于一體,能實時顯示電網的各項參數,通過鍵盤可人工設定系統運行的參數。單片機外圍芯片PSD8XX及復雜可編程邏輯器件(CPLD)的使

- 關鍵字:

CPLD 無功補償 控制儀 鍵盤設計

- EDA技術是以計算機為工具完成數字系統的邏輯綜合、布局布線和設計仿真等工作。電路設計者只需要完成對系統功能的描述,就可以由計算機軟件進行系統處理,最后得到設計結果,并且修改設計方案如同修改軟件一樣方便。利用

- 關鍵字:

VHDL FPGA 自動售貨機 控制模塊

- 一、硬件電路設計本文選用CPLD 是ALTERA 公司的EPM240T100,結合MAX232 接口芯片進行串口通信設計,框圖如下圖1 所示。

圖1 CPLD串口通信模塊硬件設計二、VHDL程序模塊設計及描述使用VHDL 對CPLD 進行編程,設計3 個

- 關鍵字:

CPLD 串口 電路設計

- 可編程邏輯器件(PLD,Programmable Logic Device)的靈活性一直受到電子工程師的喜愛,但在各種移動式消費類電子產品市場仍然是ASIC芯片的天地。有幾個原因阻礙著CPLD器件進入移動設備市場,尤其是各種基于電池供電的

- 關鍵字:

CPLD 便攜式應用 零功耗 系統

- 本設計采用可編程芯片和VHDL語言進行軟硬件設計,不但可使硬件大為簡化,而且穩定性也有明顯提高。由于可編程芯片的頻率精度可達到50 MHz,因而計時精度很高。本設計采用逐位設定預置時間,其最長時間設定可長達99小

- 關鍵字:

240C Q240 VHDL 240

vhdl-cpld介紹

您好,目前還沒有人創建詞條vhdl-cpld!

歡迎您創建該詞條,闡述對vhdl-cpld的理解,并與今后在此搜索vhdl-cpld的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473