- 1、如何選擇PCB 板材料? 對于選擇PCB板材,必須在滿足設計需求和可量產性以及成本的中間取得平衡點。設計需求包含電氣和機構這兩個部分。而通常在設計非常高速的 PCB 板子(大于 GHz 的頻率)時,這材質問題會比較重要。例如,現在常用的FR-4 材質中,在幾個GHz 的頻率時的介質損耗(dielectric loss)會對信號衰減有很大的影響,可能就不適用。而就電氣來說,要注意介電常數(dielectric

- 關鍵字:

PCB

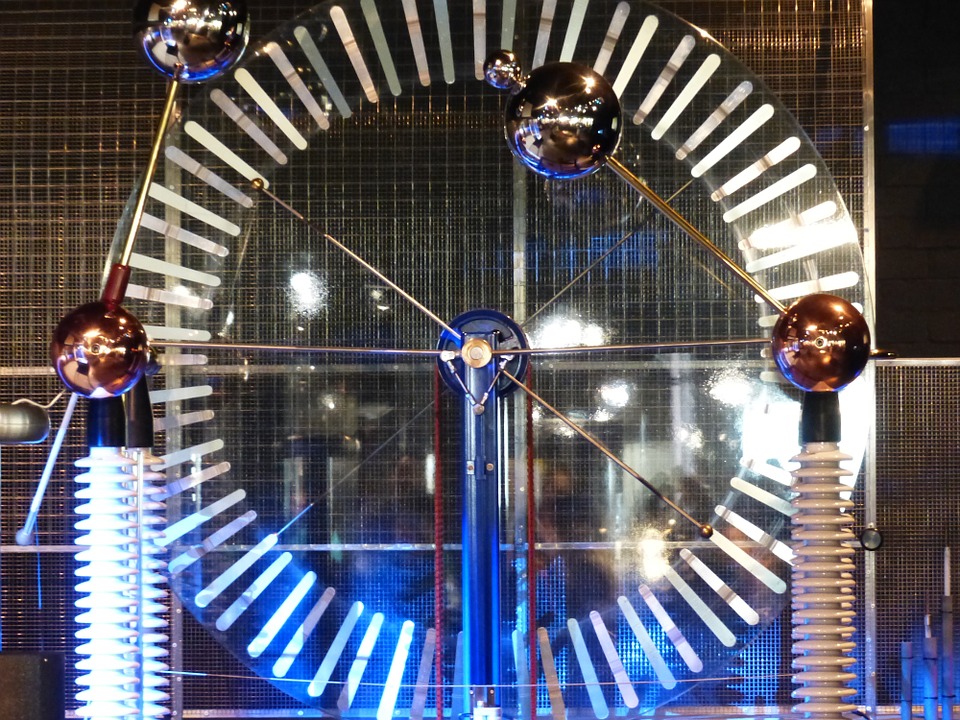

- 有人說過,世界上只有兩種電子工程師:經歷過電磁干擾的和沒有經歷過電磁干擾的。伴隨著PCB走線速遞的增加,電磁兼容設計是我們電子工程師不得不考慮的問題。面對一個設計,當進行一個產品和設計的EMC 分析時,有以下5 個重要屬性需考慮: (1) 關鍵器件尺寸:產生輻射的發射器件的物理尺寸。射頻(RF) 電流將會產生電磁場,該電磁場會通過機殼泄漏而脫離機殼。PCB 上的走線長度作為傳輸路徑對射頻電流具有直接的影響。 (2) 阻抗匹配:源和接收器的

- 關鍵字:

PCB RF

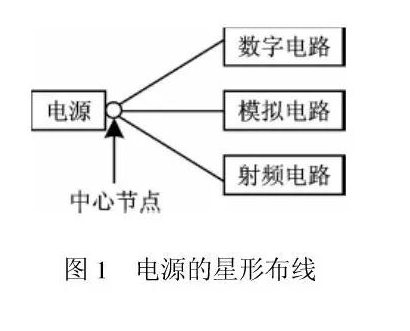

- PCB設計到軟件處理方面來介紹對電磁兼容性的處理。 一、影響EMC的因數 1、電壓:電源電壓越高,意味著電壓振幅越大,發射就更多,而低電源電壓影響敏感度。 2、頻率:高頻產生更多的發射,周期性信號產生更多的發射。在高頻單片機系統中,當器件開關時產生電流尖峰信號;在模擬系統中,當負載電流變化時產生電流尖峰信號。 3、接地:在所有EMC題目中,主要題目是不適當的接地引起的。有三種信號接地方法:單點、多點和混合。在頻率低于1MHz時,可采用單點接地方法,但不適宜高頻;在高頻應用中,最好采用多點接地。

- 關鍵字:

PCB EMI

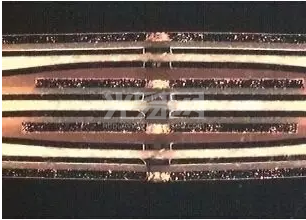

- 紫外激光器是很多工業領域中各種PCB材料應用的最佳選擇,從生產最基本的電路板,電路布線,到生產袖珍型嵌入式芯片等高級工藝都通用。這一材料的差異性使得紫外激光器成為了很多工業領域中各種PCB材料應用的最佳選擇,從生產最基本的電路板,電路布線,到生產袖珍型嵌入式芯片等高級工藝都通用。

應用1:表面蝕刻/電路生產

紫外激光器在生產電路時工作迅速,數分鐘就能將表面圖樣蝕刻在電路板上。這使得紫外激光器成為生產PCB樣品的最快方法。研發部門注意到,越來越多的樣品實驗室正在配備內部紫外激光系統。

- 關鍵字:

PCB

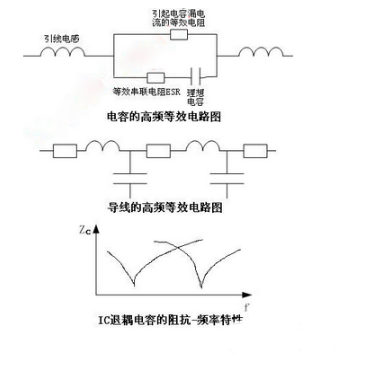

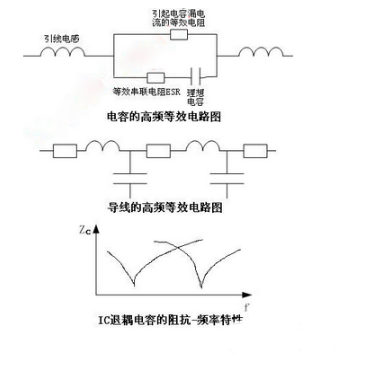

- 電磁兼容的問題常發生于高頻狀態下,個別問題(電壓跌落與瞬時中斷等)除外。高頻思維,總而言之,就是器件的特性、電路的特性,在高頻情況下和常規中低頻 狀態下是不一樣的,如果仍然按照普通的控制思維來判斷分析,則會走入設計的誤區。比如: 電容的高頻等效特性 電容,在中低頻或直流情況下,就是一個儲能組件,只表現為一個電容的特性,但在高頻情況下,它就不僅僅是個電容了,它有一個理想電容的特性,有漏電流(在 高頻等效電路上表現為R),有引線電感,還在導致電壓脈沖波動情況下發熱的ESR(等效串聯

- 關鍵字:

電磁兼容 PCB

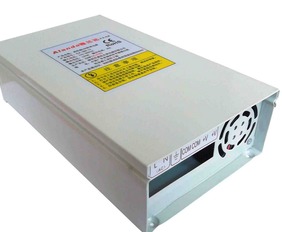

- 對于開關電源的研發,PCB設計占據很重要的地位。一個差的PCB,EMC性能差、輸出噪聲大、抗干擾能力弱,甚至連基本功能都有缺陷。 與其他硬件電路PCB稍有不同,開關電源PCB有一些自身的特點。本文將結合工程經驗,簡單談一談開關電源PCB布線的一些最基本的原則。 1、間距 對于高電壓產品必須要考慮到線間距。能滿足相應安規要求的間距當然最好,但很多時候對于不需要認證,或沒法滿足認證的產品,間距就由經驗決定了。多寬的間距合適?必須考慮生產能否保證板面清潔、環境濕度、其他污染等情

- 關鍵字:

開關電源 PCB

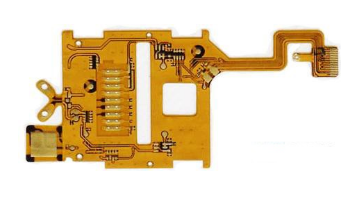

- 電子產品都要使用PCB,PCB的市場走向幾乎是電子行業的風向標。隨著手機、筆記本電腦和PDA等高端、小型化電子產品的發展,對柔性PCB(FPC)的需求越來越大,PCB廠商正加快開發厚度更薄、更輕和密度更高的FPC,小編來跟大家簡介FPC的種類。 一、單層FPC

具有一層化學蝕刻出的導電圖形,在柔性絕緣基材面上的導電圖形層為壓延銅箔。絕緣基材可以是聚酰亞胺,聚對苯二甲酸乙二醇酯,芳酰胺纖維酯和聚氯乙烯。單層FPC又可以分成以下四個小類: 1.無覆蓋層單面

- 關鍵字:

FPC PCB

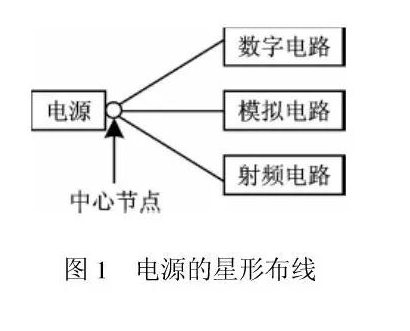

- 單片射頻器件大大方便了一定范圍內無線通信領域的應用,采用合適的微控制器和天線并結合此收發器件即可構成完整的無線通信鏈路。它們可以集成在一塊很小的電路板上,應用于無線數字音頻、數字視頻數據傳輸系統,無線遙控和遙測系統,無線數據采集系統,無線網絡以及無線安全防范系統等眾多領域。 1 數字電路與模擬電路的潛在矛盾 如果模擬電路(射頻) 和數字電路(微控制器) 單獨工作可能各自工作良好,但是一旦將兩者放在同一塊電路板上,使用同一個電源供電一起工作,整個系統很可能就會不穩定。這

- 關鍵字:

PCB RF

- 2017國際線路板及電子組裝華南展覽會(2017 HKPCA & IPC Show)將于2017年12月6至8日再次在中國深圳會展中心舉行。今年展會以“智慧大匯,實地創成”為主題,體現展會的愿景——匯聚全球智慧,幫助業內企業將全球的高端技術應用于當地實際生產,從而有效提升業務發展。 展商反響熱烈,展會規模創歷史新高 2017年展商對展位的需求非常熱烈。截至7月份,今年展會97%的展位已銷售一空,而且還有眾多展商報名參展,反響十分熱烈。截至目前,本屆展

- 關鍵字:

線路板 PCB

- 1.引言 一個良好的布局設計可優化效率,減緩熱應力并盡量小走線與元件之間噪聲作用。這切都 源于設計人員對電中流傳導路徑以及信號的理解。 當一塊原型電源板首次加時,最好的情況 是它不僅能工作而且還安靜、發熱低。然這種并不多見。 開關電源的一個常見問題是 “不穩定 ”的開關波形。有些時候,抖動處于聲段磁性元件會產生 出音頻噪聲。如果問題在印刷電路板的布局上, 要找原因可能會很困難此開關電源 設計初期的 正確 P

- 關鍵字:

開關電源 PCB

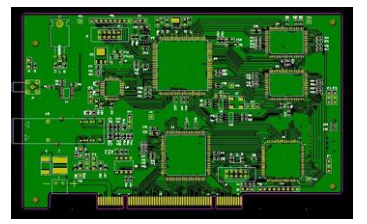

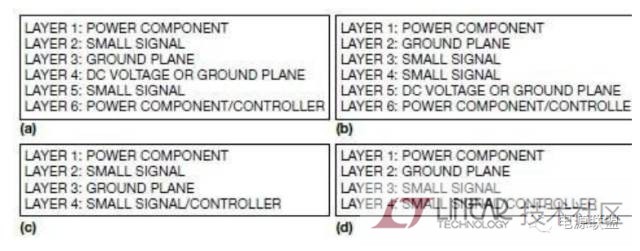

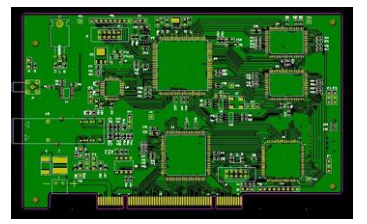

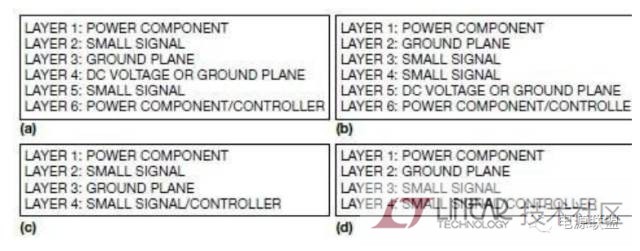

- 在開始布線之前應該對設計進行認真的分析以及對工具軟件進行認真的設置,這會使設計更加符合要求。 1 確定PCB的層數 電路板尺寸和布線層數需要在設計初期確定。布線層的數量以及層疊(STack-up)方式會直接影響到印制線的布線和阻抗。板的大小有助于確定層疊方式和印制線寬度,實現期望的設計效果。目前多層板之間的成本差別很小,在開始設計時最好采用較多的電路層并使敷銅均勻分布。 2 設計規則和限制 要順利完成布線任務,布線工具需要在正確的規則和限制條件下工作。要對所有特殊要求的信號

- 關鍵字:

PCB

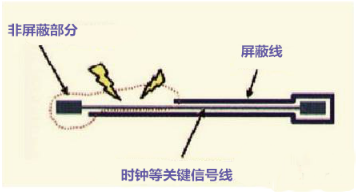

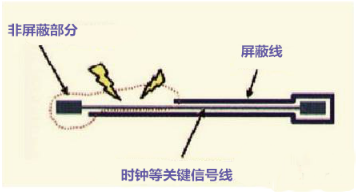

- 規則一:高速信號走線屏蔽規則 在高速的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。 圖1 高速信號線 規則二:高速信號的走線閉環規則 由于PCB板的密度越來越高,很多PCB LAYOUT工程師在走線的過程中,很容易出現一種失誤,即時鐘信號等高速信號網絡,在多層的PCB走線的時候產生了閉環的結果,這樣的閉環結果將產生環形天線,增加EMI的輻射強度。 圖2 閉環

- 關鍵字:

PCB 硬件工程師

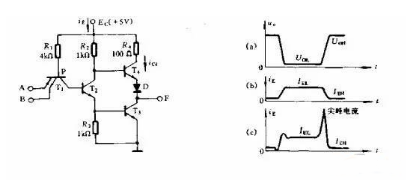

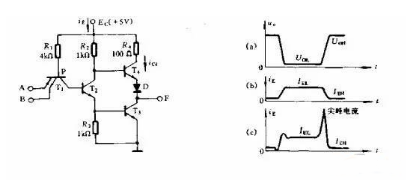

- 尖峰電流的形成: 數字電路輸出高電平時從電源拉出的電流Ioh和低電平輸出時灌入的電流Iol的大小一般是不同的,即:Iol>Ioh。以下圖的TTL與非門為例說明尖峰電流的形成:

圖1 TTL與非門 輸出電壓如右圖(a)所示,理論上電源電流的波形如右圖(b),而實際的電源電流保險如右圖(c)。由圖(c)可以看出在輸出由低電平轉換到高電平時電源電流有一個短暫而幅度很大的尖峰。尖峰電源電流的波形隨所用器件的類型和輸出端所接的電容負載而異。 產生尖峰電流的

- 關鍵字:

PCB 去耦電容

- 20世紀后半期,隨著集成電路和計算機技術的發展,數字系統也得到了飛速發展,其實現方法經歷了由分立元件、SSI、MSI到LSI、VLSI以及UVLSI的過程。同時為了提高系統的可靠性與通用性,微處理器和專用集成電路(ASIC)逐漸取代了通用集成硬件LSI電路,而在這兩者之間,ASIC以其體積小、重量輕、功耗低、速度快、成本低、保密性好而脫穎而出。總的來說,ASIC的制作可粗略地分為掩膜式方法和現場可編程方法兩大類。目前,業界大量可編程器件(PLD),尤其是現場可編程邏輯器件(CPLD/FPGA)被大量地

- 關鍵字:

EDA PCB

- 半個世紀以來,靜電在電子行業引起的著火、爆炸等事故不勝枚舉。僅美國電子行業每年因靜電造成的損失就高達幾百億美元,因此,靜電防護在減少損失、提升品質和消費效率方面具有重要的意義。

隨著集成電路行業的迅速發展,體積小、集成度高的器件越發受市場歡迎,這種需求也導致導線間間距越來越小,內部氧化膜逐漸變薄,以至于制造過程中一些微小電壓就可能擊穿這些電子器件。而電子產品在生產、運輸、儲存和轉運等一系列過程中所產生的靜電電壓卻遠遠超過其耐壓值,這就可能造成器件的擊穿或失效,影響產品的可靠性。所以必須要重視靜電

- 關鍵字:

靜電 PCB

rf-pcb介紹

您好,目前還沒有人創建詞條rf-pcb!

歡迎您創建該詞條,闡述對rf-pcb的理解,并與今后在此搜索rf-pcb的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473