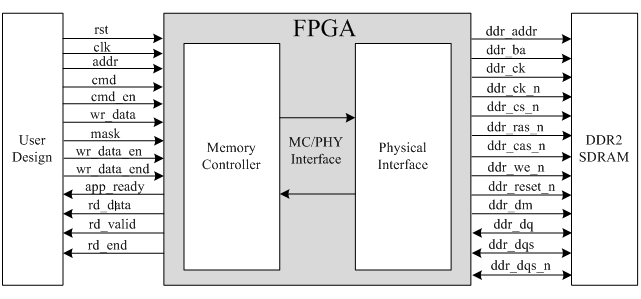

山東濟南,2017年10月10日訊,山東高云半導體科技有限公司(以下簡稱“山東高云半導體”)今天宣布推出基于中密度晨熙?家族的GW2A系列FPGA芯片的DDR類儲存器接口IP核初級版(Gowin Memory Interface IP),包括相關IP軟核、參考設計及開發板等完整解決方案。 高云DDR類儲存器接口IP核初級版目前是一個通用的DDR2存儲器接口IP,兼容JESD79-2標準。該IP包含通用的DDR2內存控制器(Memory Controller,M

關鍵字:

高云 FPGA

某些FPGA終端,包含板載的、可以動態隨機訪問的存儲塊(DRAM),這些存儲塊可以在FPGA VI中直接訪問,速率非常高。 DRAM可以用來緩存大批量的數據,而且速度可以非常快。針對一些特殊應用,比如:瞬時帶寬非常高,而且有要保存原始數據的時候,就可以用DRAM做一個大的FIFO緩沖。 DRAM的大小每塊板卡可能不同,一般在官網中對應板卡的說明中都會標明DRAM的大小(如果有DRAM的話)。比如,PXIe-7966R就有512M的DRAM空間。 http://sine.ni.com/n

關鍵字:

FPGA DRAM

萊迪思半導體公司,客制化智能互連解決方案市場的領先供應商,今日宣布廣東虛擬現實科技有限公司(Ximmerse),移動AR/VR應用交互系統提供商,選擇采用萊迪思ECP5? FPGA為其AR/VR跟蹤平臺實現立體視覺計算解決方案。得益于低功耗、小尺寸和低成本的優勢,市場領先的萊迪思ECP5 FPGA是用于實現網絡邊緣靈活的互連和加速應用的理想選擇,可實現低功耗、低延遲的解決方案。 隨著對于AR/VR設備市場需求的不斷增長,目前基于頭戴式顯示器(HMD)的系統在使用移動應用處理器(A

關鍵字:

Ximmerse FPGA

當下時代的主題究竟是什么?5G通信?人工智能?自動駕駛?還是云計算?或許都是;又或許,都不是。當你看到在這些前端應用市場不斷迸發著激情和靈感時,如何滿足其背后以指數形式增長的數據需求就成了諸多工程師最為頭疼的問題。

關鍵字:

英特爾,FPGA,智能互聯

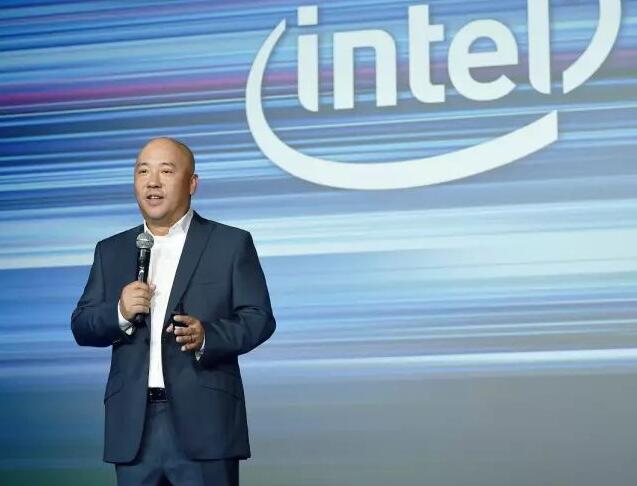

“英特爾精尖制造日”活動今天舉行,展示了英特爾制程工藝的多項重要進展,包括:英特爾10納米制程功耗和性能的最新細節,英特爾首款10納米FPGA的計劃,并宣布了業內首款面向數據中心應用的64層3D NAND產品已實現商用并出貨。

英特爾公司全球副總裁兼中國區總裁楊旭 歡迎來自合作伙伴、客戶、政府部門和學術界的嘉賓以及新聞媒體出席2017年9月19日在北京舉行的“英特爾精尖制造日”活動。此次活動著眼于快速發展的中國技術生態系統,重申英特爾與中國半導體產業共成長

關鍵字:

英特爾 FPGA

萊迪思半導體公司(NASDAQ: LSCC),客制化智能互連解決方案市場的領先供應商,今日宣布Valve采用萊迪思的低功耗、低成本iCE40? FPGA為SteamVR?跟蹤平臺實現實時數據采集和處理功能。 作為SteamVR跟蹤平臺上的低功耗、低延遲傳感器中心,萊迪思iCE40 FPGA大大減少了傳感器到應用處理器/微控制器的印刷電路板(PCB)信號布線數量,從而降低EMI干擾和PCB擁塞程度,并提高信號完整性。 萊迪思半導體資深業務發展經理陳英仁表示:“我們的低功

關鍵字:

萊迪思 FPGA

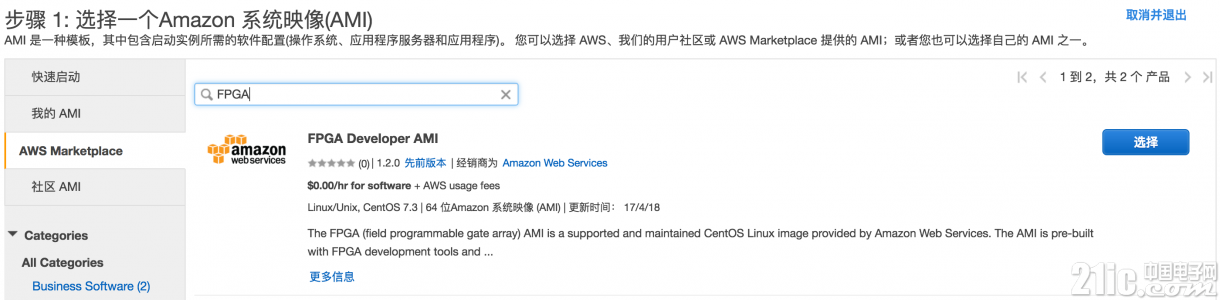

前言 在4月19號的舊金山AWS技術峰會上,亞馬遜CTO Werner Vogels宣布了多項AWS新功能,其中就包括眾人期待已久的FPGA實例F1。 F1 實例配有最新的 16 nm Xilinx UltraScale Plus FPGA,目前有f1.2xlarge和f1.16xlarge兩種類型,其中f1.2xlarge配備有1個FPGA卡, f1.16xlarge配備有8個FPGA卡。 使用

關鍵字:

FPGA 神經網絡

這里談談一些經驗和大家分享,希望能對IC設計的新手有一定的幫助,能使得他們能少走一些彎路!

在IC工業中有許多不同的領域,IC設計者的特征也會有些不同。在A領域的一個好的IC設計者也許會花很長時間去熟悉B領域的知識。在我們職業生涯的開始,我們應該問我們自己一些問題,我們想要成為怎樣的IC設計者?消費?PC外圍?通信?微處理器或DSP?等等。

IC設計的基本規則和流程是一樣的,無論啥樣的都會加到其中。HDL,FPGA和軟件等是幫助我們理解芯片的最好工具。IC的靈魂是知識。因此我們遇到的第一個

關鍵字:

FPGA

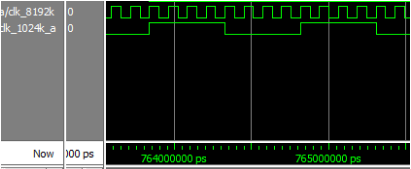

1. 概述 隨著集成電路技術的快速發展,半導體存儲、微處理器等相關技術的發展得到了飛速發展。FPGA以其可靠性強、運行快、并行性等特點在電子設計中具有廣泛的意義。作為一種可編程邏輯器件,FPGA在短短二十年中從電子設計的外圍器件逐漸演變為數字系統的核心。伴隨著半導體工藝技術的進步,FPGA器件的設計技術取得了飛躍發展及突破。 分頻器通常用來對某個給定的時鐘頻率進行分頻,以得到所需的時鐘頻率。在設計數字電路中會經常用到多種不同頻率的時鐘脈沖,一般采用由一個固定的晶振時鐘頻率來產生所需要的不

關鍵字:

FPGA 數字分頻器

人工智能算法的實現需要強大的計算能力支撐,特別是深度學習算法的大規模使用,對計算能力提出了更高的要求。而從人工智能芯片所處的發展階段來看,從結構層面去模仿大腦運算雖然是人工智能追求的終極目標,但距離現實應用仍然較為遙遠,功能層面的模仿才是當前主流。

關鍵字:

人工智能 FPGA

現有的可穿戴設備大部分都是智能手表或健康手環。這些應用本質上并不“智能”,而是對智能手機的擴展,用于輕松訪問副屏和/或進行低速和低功耗生理體征測量,如計步器和心率測量等。隨著語音、AR和AI技術的發展,我們將會看到更多更加智能的可穿戴設備,涵蓋語音控制的智能耳機到可以進行空間、手勢和目標識別的AR眼鏡。這些全新的應用,特別是涉及到空間測量(例如音頻波束形成或AR手勢檢測)時,需要實時工作的低功耗傳感器中心來同時捕捉和處理來自傳感器陣列的數據。與其他應用處理器、MCU和DSP相比,萊迪思FPGA能夠提供靈活

關鍵字:

可穿戴 FPGA 萊迪思

自從機器學習(machinelearning;ML)與人工智能(AI)在近期受到歡迎后,包括英特爾(Intel)等科技大廠也積極抓緊機會投入開發相關領域。該公司高層日前也表示,英特爾正利用現場可編程閘陣列(FPGA)技術,提供ML或AI的解決方案。據NewElectronics報導,為了搶搭ML與AI風潮,英特爾透過收購與內部發展打造解決方案。英特爾的可編程系統事業群(ProgrammableSystemsGroup;PSG)前身為Altera,AI產品專家BillJenkins表示,PSG專注在機器

關鍵字:

英特爾 FPGA

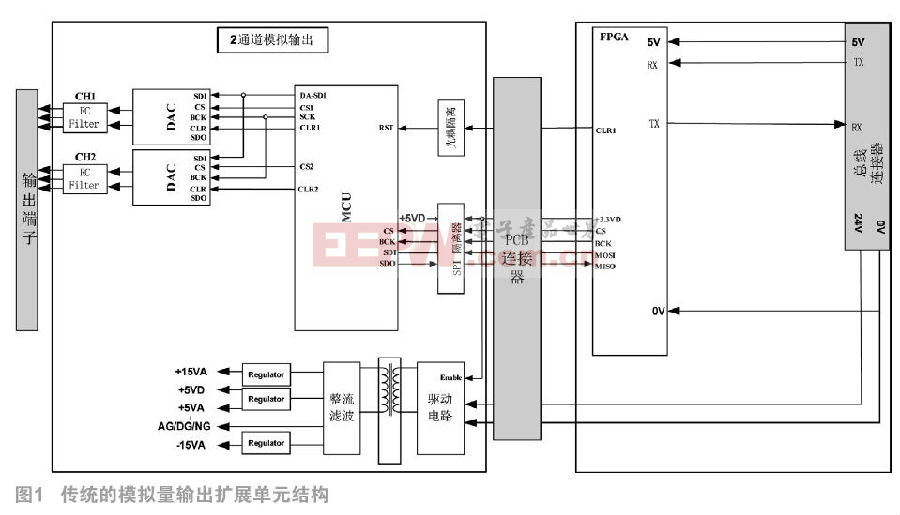

本文設計了一種以FPGA為核心,基于AD5422實現多路高精度輸出的PLC模擬量擴展單元模塊。設計先對現有的方案進行了分析和討論,之后對FPGA內部相關處理機制和實現方案做了詳盡的論述,經過仿真和測試驗證了設計的可行性。相比于傳統的模擬量擴展單元模塊,本系統具有處理速度快、方便、靈活,電路精簡,抗干擾能力強等優點。

關鍵字:

FPGA AD5422 串行外設接口 201709

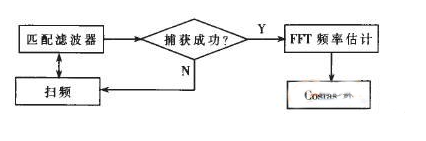

在高動態環境中,由于載波多普勒頻移和收發端時鐘漂移等因素的存在,直擴接收機必須通過載波同步才能在接收端消除頻差并重構載波相位,以實現相干解調。在傳統的載波同步技術中,鎖頻環具有較大的捕獲帶寬但頻率跟蹤精度相對較低;鎖相環雖然具有較高的跟蹤精度卻受到捕獲帶寬的限制。在同步時間要求不高的通信系統中,可以采用鎖頻環與鎖相環級聯的載波同步方法,使接收機既能承受環路帶寬與動態性能之間的折中,又同時滿足跟蹤精度和一定動態性能。但本文所涉及的短時猝發式擴頻通信系統要求更大的捕獲帶寬(±30kHz),且導頻符號僅為2

關鍵字:

FPGA 載波同步

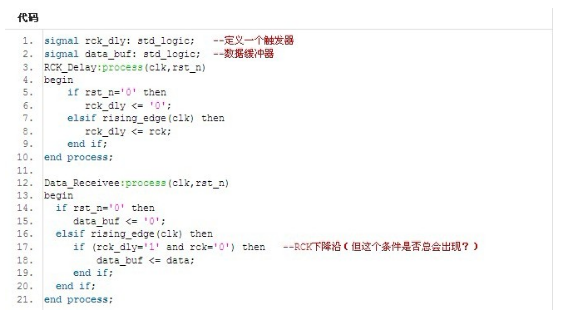

在同步電路設計中,邊沿檢測是必不可少的! 例如:在一個時鐘頻率16MHz的同步串行總線接收電路里,串行總線波特率為1Mbps。在串行總線的發送端是在同步時鐘(1MHz)的上升沿輸出數據,在接收端在同步時鐘的下降沿對輸入數據進行接收采樣。在這個接收電路里檢測同步時鐘的下降沿是必不可少的。假設主時鐘-clk,同步時鐘-rck,同步數據-data。 有些人在邊沿檢測的時候就喜歡這樣做:

但是大家忽略了一種情況,就是clk與rck之間比沒有必然的同步關系,當r

關鍵字:

FPGA 邊沿檢測

fpga介紹

FPGA是英文Field-Programmable Gate Array的縮寫,即現場可編程門陣列,它是在PAL、GAL、EPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。

FPGA采用了邏輯單元陣列LCA(Logic Cell Array)這樣一個新概念,內部包括可 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473