- 基于SRAM的FPGA由于其可編程、可升級的特性,被廣泛應用于現代通信系統中。由于其易失性,每次上電后都需要重新對FPGA進行加載。隨著通信系統復雜度的提高,FPGA配置文件越來越大,加載時間越來越長,嚴重影響系統的啟動時同。為了提高FPGA的加載效率,在此提出一種通過CPLD進行FPGA串行加載的方案。通過驗證,該方法既能能提高FPGA加載效率,又能節省CPU和FPGA的GIPO管腳,降低系統啟動時間,非常適用于現代復雜通信系統。

- 關鍵字:

CPLD FPGA

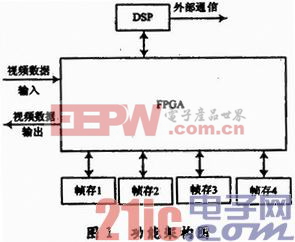

- 面向異步視頻的嵌入式圖像處理系統設計,摘要:在此設計出一種基于DSP+FPGA技術的面向異步視頻的嵌入式圖像處理系統,以一種靈活的架構避免了幀間不同步方法對雙口RAM顯存的需求,既能夠保證圖像輸出質量,又有利于提升圖像處理的性能指標。系統以FPGA為核心

- 關鍵字:

異步視頻 圖像處理 嵌入式系統 FPGA 幀存切換

- 引言

SRAM有高速和不用刷新等優點,被廣泛用于高性能的計算機系統。由于半導體工藝技術的提高以及存儲系統多方面的需要,存儲器件日益向高速、高集成方向發展,在使系統功能強大的同時,也增加了系統的復雜性

- 關鍵字:

FPGA SRAM 自測試

- HDTV視頻內容創作的繁榮以及在帶寬受限的廣播信道環境中傳送這些視頻內容的方法,不斷催生新的視頻壓縮標準和...

- 關鍵字:

FPGA 廣播視頻 HDTV

- 基于SoPC的狀態監測裝置的嵌入式軟硬件協同設計,摘要:首先介紹了軟硬件協同設計方法的發展過程和狀態監測裝置開發的背景資料,然后利用該方法設計了一款新型的高性能狀態監測裝置,并分別從硬件和軟件2個角度對設計方法進行了深入說明。該裝置已成功集成于水電機組

- 關鍵字:

軟硬件協同 SoPC 狀態監測 Linux FPGA PLC

- 據報道,Microsemi公司SoC產品集團(原Actel公司)開發的RTAX-DSP現場可編程門陣列(FPGA)器件已獲得合格制造商清單(QML)V類和Q類資格認證,這意味著該FPGA器件獲準用于衛星、載人飛船和其他空間應用。

公司官方表示,Microsemi的抗輻射QML-V FPGA在不同程度上能夠承受空間自然輻射影響,并對每個特定晶片都進行2,000小時的壽命測試,對每個特定組件都進行破壞性物理分析。

RTAX-DSP FPGA將復雜數字信號處理(DSP)功能集成到單一設備,滿足高

- 關鍵字:

Microsemi FPGA

- 引言短波通信是一種能進行遠距離傳輸,而對電臺的要求相對較低的通信系統。短波具有的遠距離通信能力和電臺具有的較高機動性等特點,使其在軍事通信領域中具有重要的應用價值。然而,短波信道頻帶窄,傳播特性不穩定

- 關鍵字:

FPGA DSP 短波擴頻 通信系統

- 0 引言IIR數字濾波器在很多領域中都有著廣闊的應用。與FIR數字濾波器相比,IIR數字濾波器可以用較低的階數獲得較高的選擇性,而且所用存儲單元少,經濟效率高。一個N階IIR數字濾波器的系統函數為: 其線性常系數差分

- 關鍵字:

FPGA IIR 數字濾波器

- FPGA/CPLD的設計流程 1、電路設計與輸入 電路設計與輸入是指通過某些規范的描述方式,將工程師電路構思輸入給EDA工具。常用的設計方法有硬件描述語言(HDL)和原理圖設計輸入方法等。原理圖設計輸入法在早期應用得比

- 關鍵字:

FPGA 設計流程 布線 資源

- 摘要:本文以微控制器AT91RM9200 和EP1C6Q240C8 為核心,對工業CT 機的運動控制器進行了設計,從硬件和軟件兩個方 ...

- 關鍵字:

ARM FPGA 運動控制器

- 大多數的勘探、觀測工作都是在嚴苛的環境中進行的,對數據的準確性、實時性都有著較高的要求,并且大多情況 ...

- 關鍵字:

ARM FPGA 同步數據采集

- 2012年12月13日,Altera聯合ARM召開發布會,共同宣布發售其首款28nm FPGA SoC器件,包含雙核ARM Cortex-A9 800MHz處理器,此時,賽靈思的類似產品Zynq已經發售一年有余。

客觀來說,Altera的SoC產品進展比賽靈思緩慢許多,2010年,賽靈思就放出了與ARM合作開發下一代SoC器件的消息,而與之對應的Altera只是公布了與MIPS的合作藍圖,又聯合Intel宣布X86與FPGA的融合技術,直到2011年年中,Altera與ARM的合作計劃才姍姍來遲

- 關鍵字:

Altera FPGA

- 美國國家儀器公司(National Instruments, 簡稱 NI)近日發布用于NI FlexRIO的NI 5791射頻收發儀適配器模塊,目前多個機構都在使用該收發儀進行5G技術最前沿的項目研究。 該模塊搭配NI FlexRIO FPGA,用于實時、用戶設計的處理,形成了一個強大的SDR解決方案。

- 關鍵字:

NI FPGA 軟件

- 引言 Adaboost 算法是Freund 和Schapire 于1995 年提出的,全稱為Adaptive Boosting。它是 Boosting 算法的改進,意為該算法通過機器訓練與學習不斷自適應地調整假設的錯誤率,這 種靈活性使得Adaboost 算法很容易

- 關鍵字:

Adaboost FPGA 算法 性能分析

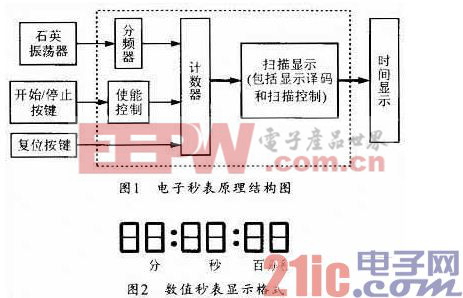

- 基于FPGA的數字秒表設計與仿真,數字集成電路作為當今信息時代的基石,不僅在信息處理、工業控制等生產領域得到普及應用,并且在人們的日常生活中也是隨處可見,極大的改變了人們的生活方式。面對如此巨大的市場,要求數字集成電路的設計周期盡可能

- 關鍵字:

仿真 設計 數字秒表 FPGA 基于

fpga-to-asic介紹

您好,目前還沒有人創建詞條fpga-to-asic!

歡迎您創建該詞條,闡述對fpga-to-asic的理解,并與今后在此搜索fpga-to-asic的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473